# MEDIATEK

# MT6516 Design Notice V1.0

2009 / April

WCP/SA

Copyright © MediaTek Inc. All rights reserved.

# **Change Notice**

- 2009/05/11 Initial document

- 2009/06/22 Add IQ 510ohm

### **Outline**

- MT6516 Main Features & Package

- Design Notice

- MT6516 schematic design notice

- PMIC MT6326 design notice

- Audio part design notice

- Speech part design notice

- Camera design notice

- Display design notice

- DDR memory layout rule

- USB 2.0 high speed design notice

- Factory Mode and Engineer Mode

- Download and META Link

- MT6516 Memory Support Plan

- Appendix Peripherals Design Notice

- WIFI/BT Co-module Application Note

- MT3326 GPS application note

- DTV part design note

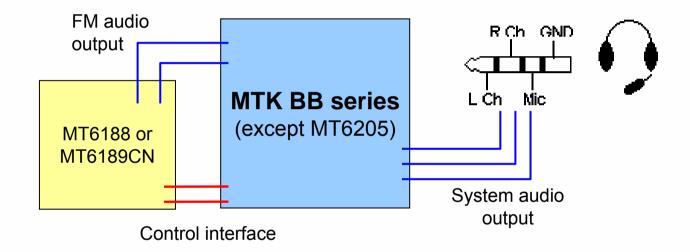

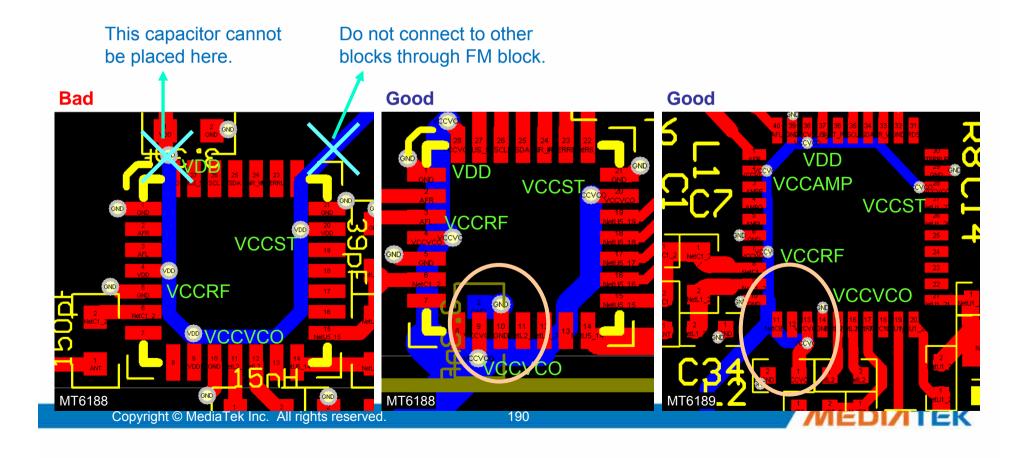

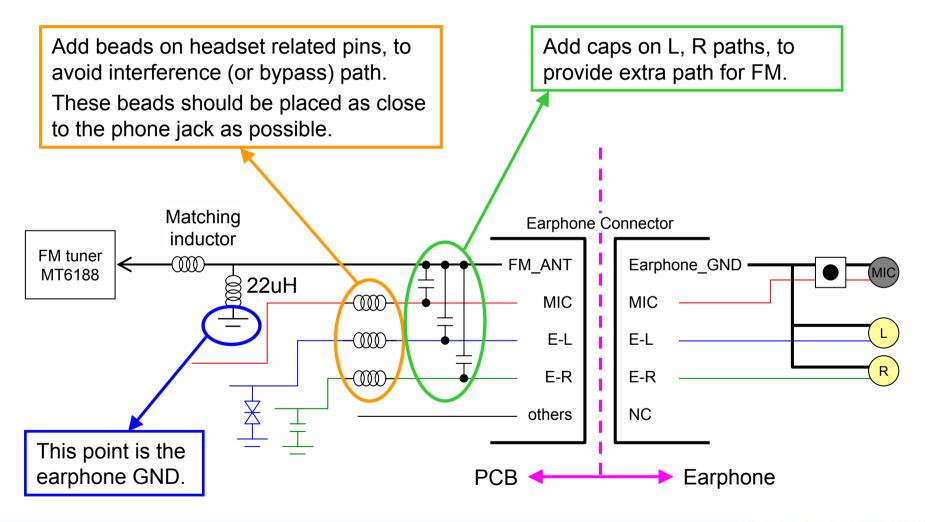

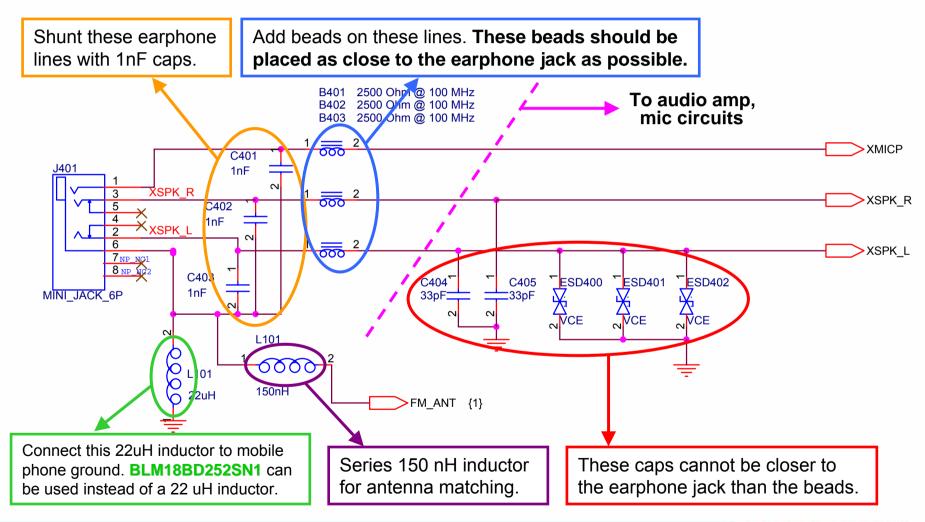

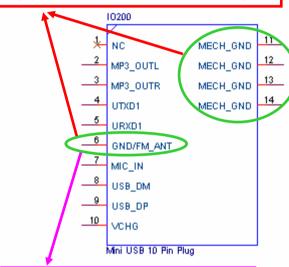

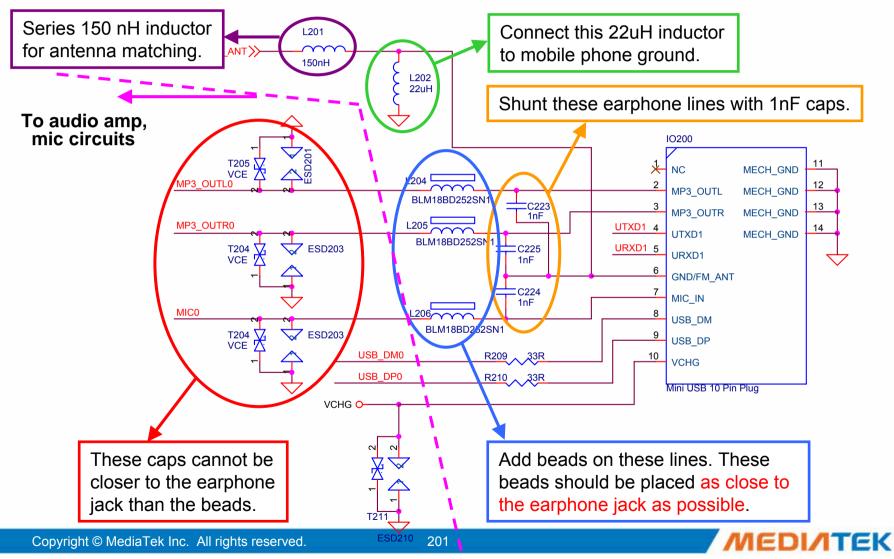

- FM design notice

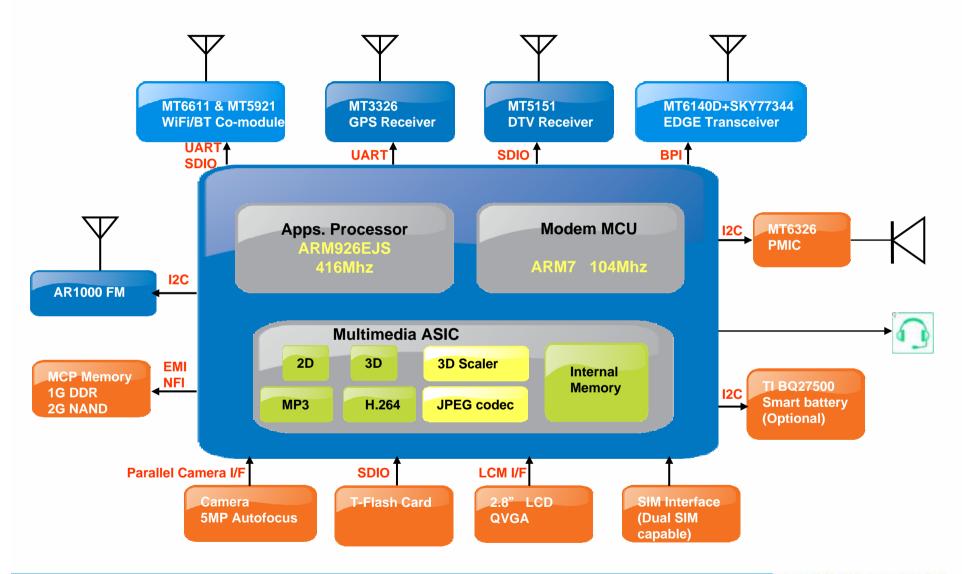

### MT6516 Main Feature

- Separate Application (ARM9) and hard real-time

Modem (ARM7)

- Multi-Cores with HW coprocessors SoC

- Application: ARM926EJS 416MHz

- Modem: ARM7 (52MHz/104MHz) + 2 DSP(104MHz)

- CEVA DSP (312MHz) for video and unpredictable multimedia application on Smartphone

- 65nm process. Ultra low power design.

- Graphics, Display, Image, Camera, Video multimedia hardware accelerators.

- 2D Graphics support Window Mobile Bitblt function

- 3D Graphics Support OpenGL ES 1.1 Common/Common Lite profile

- 3D Performance: fill rate = 32M, triangle rate = 3.7M

- Wide range of resolution up to WVGA size

- Various display Interface Support

- 8080 host IF (MIPI DBI)

- 8/9/16/32-bit Serial IF

- RGB interface (MIPI DPI)

- MIPI DSI interface

- High Performance Memory controller @ 104MHz, support

- 32-bit / 16-bit LP-DDR SDRAM

- 4 chip selects: support up to 4 DRAM devices

- NAND-boot supported

- NAND data storage supported

- Peripherals

- Dual SIM

- 3 x SDIO, 3 x I2C, 1 x I2S, 4 x UART

- 1-wire interface, 7 x PWM

- 8 x 8 Key Matrix

- Touch panel interface

- USB 2.0 high speed integrate with PHY.

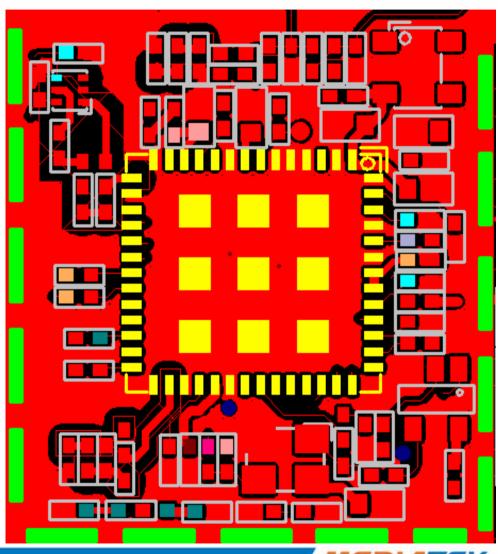

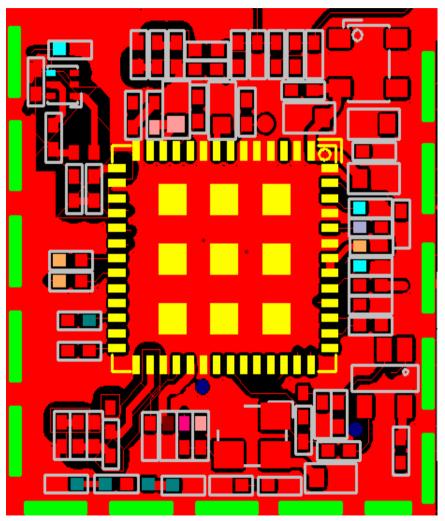

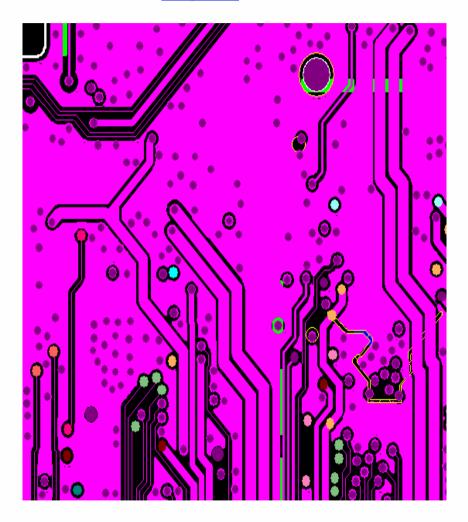

# MT6516 Design Package Building Blocks

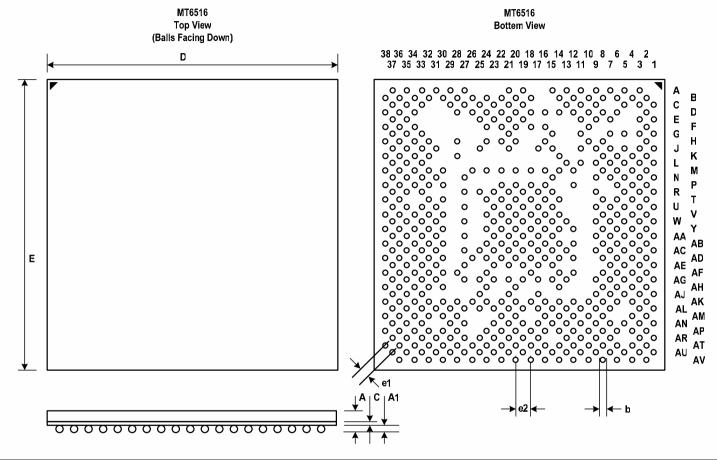

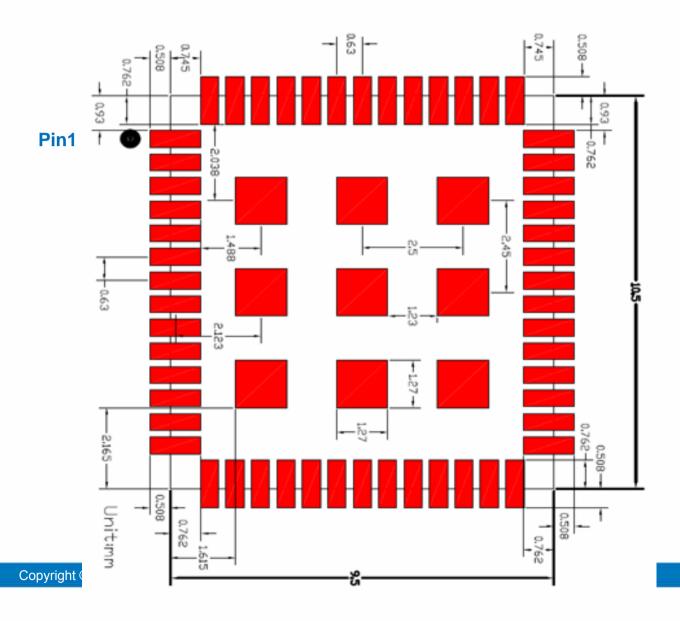

# MT6516 Package

| <b>Body Size</b> |    | Ball Count | Ball Pitch    | Ball Dia. | Package Thk. | Stand Off | Substrate Thk. |

|------------------|----|------------|---------------|-----------|--------------|-----------|----------------|

| D                | Е  | N          | e1 / e2       | b         | A (Max.)     | A1        | С              |

| 15               | 15 | 564        | 0.378 / 0.535 | 0.3       | 1.2          | 0.21      | 0.26           |

# MEDIATEK

# Design Notice - MT6516 Schematic Design Notice

Copyright © MediaTek Inc. All rights reserved.

# Schematic Notice (1/7): Boot-up selection

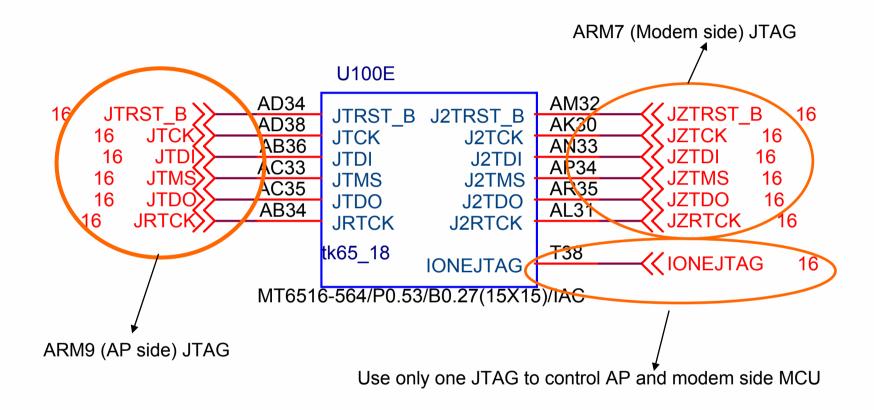

| Pin H\L    | H(DVDD)                  | L(GND)                 |  |

|------------|--------------------------|------------------------|--|

| IONEJTAG   | Enable one JTAG function | Disable                |  |

| IBOOT      | boot from external memor | boot from bootrom      |  |

| SECU_EN    | Enable secure booting    | Disable                |  |

| IADMUX     | ADMux memory device      | AD-Demux memory device |  |

| ICORESIGHT | Coresight enable,        | Coresight disable      |  |

| FSOURCE    | burn efuse               | Normal                 |  |

•MT6516 currently only support DDR memory, so this selection always choose GND

•Connect FSOURCE to GND by **0ohm**, otherwise the UUID number will be unstable.

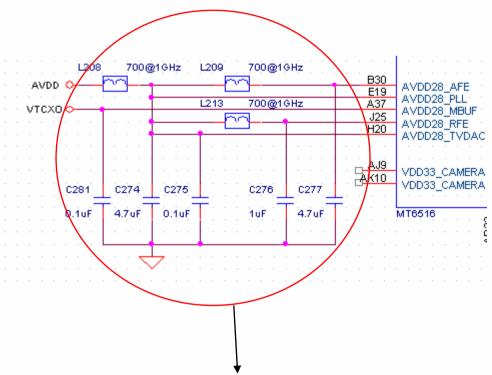

# Schematic Notice (2/7)

The AVDD Power must follow the connection show above to avoid the influence between AFE, RFE and MBUF

# Schematic Notice (3/7)

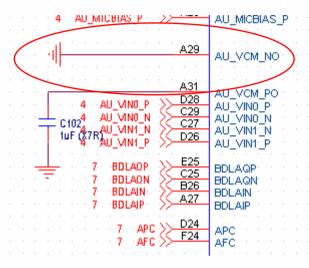

Connect AU\_VCM\_NO to GND

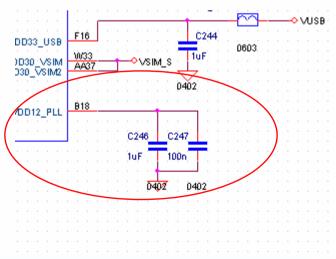

Add 2 capacitors (1uF, 0.1uF) in AVDD12\_PLL

# **Schematic Notice (4/7)**

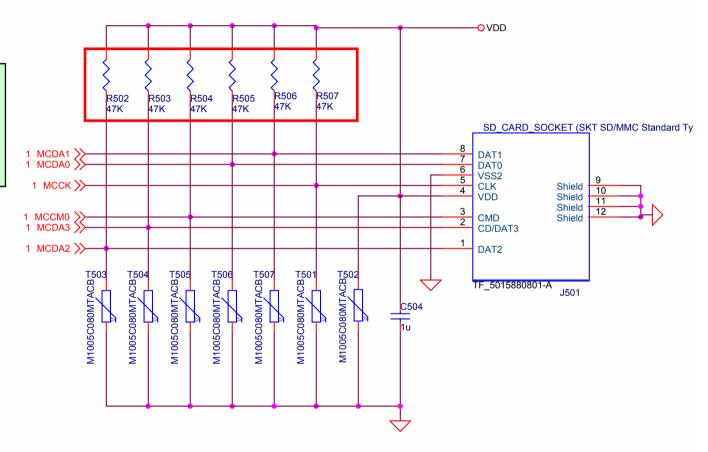

•For better interoperability and stability, please reserve 47k ohm in each memory card interface line.

# Schematic Notice (5/7)

# Schematic Notice (6/7): Debug Port

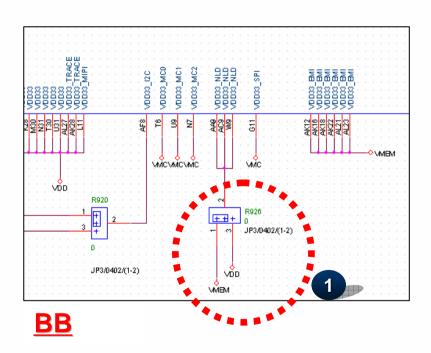

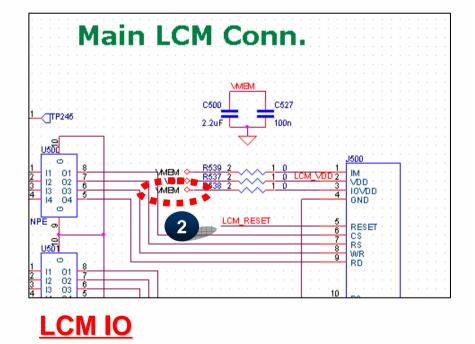

## Schematic Notice (7/7): NFI Interface

- To support 1.8 V NAND MCP, you need to

- Connect VDD33\_LCD of BB part to 1.8 V

- Check if LCM module IO can support 1.8V first. Connect LCM IO power pin (VDDIO) to 1.8 V (see <u>LCM Selection Guide to 1.8 V LCM</u> section)

Beware that NAND flash, parallel LCM, and VDD33\_NLD must use same power domain!

# RF IQ Connection (Remember add 510ohm Between Baseband and MT6140D)

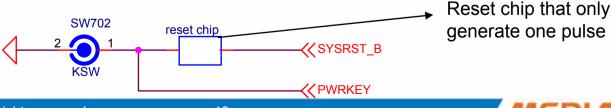

# **Reset Button Design Suggestion**

- 1. Basically, the MT6516 phone don't need reset button. (Users remove battery when system hang)

- 2. There are two kinds of suggestion design of reset button.

- 1. Only add a pull low button on SYSRST\_B pin

- 1. Advantage : cost effective

- 2. Disadvantage: User must press pwrkey to restart system

- 2. Add a reset chip on pwrkey pin and SYSRST\_B pin.

- 1. Advantage : User can press reset then direct restart the phone.

- Disadvantage : Need a extra reset chip

# **Default UART Dispatch Notice**

**UART1**

Download Bootloader, META Link, Production Line Test Point

User Define, Default Use for AGPS

**UART3**

User Define, Default Use for Bluetooth

Data Log for Debugging, Boot-Up Selection and Setting. Modem side META link.

Download Image BIN file, Active Sync, Mass Storage, RNDIS

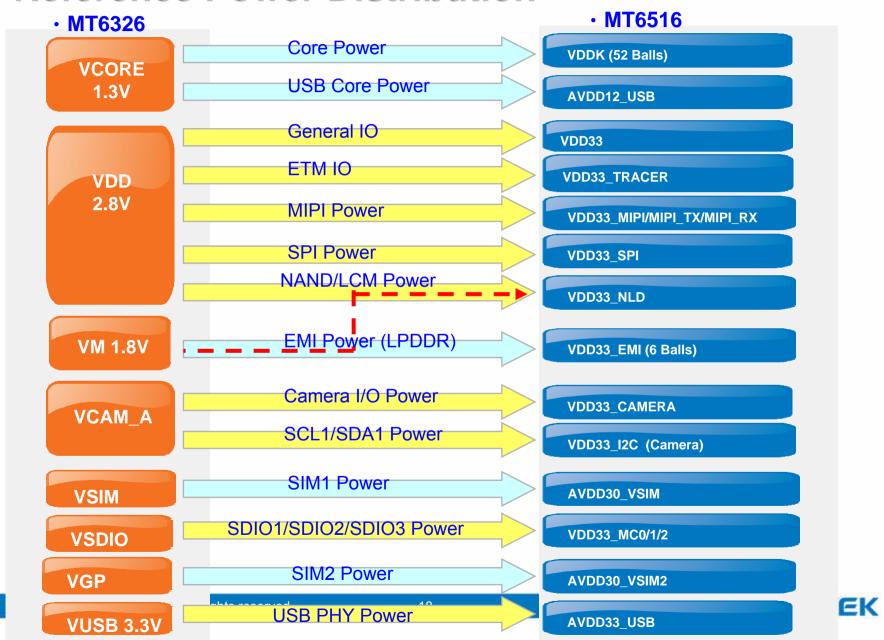

### **Reference Power Distribution**

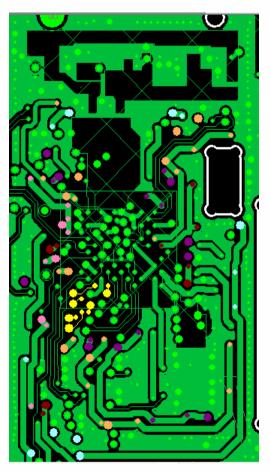

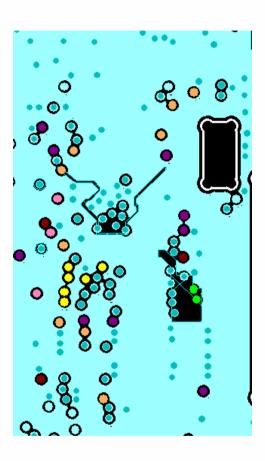

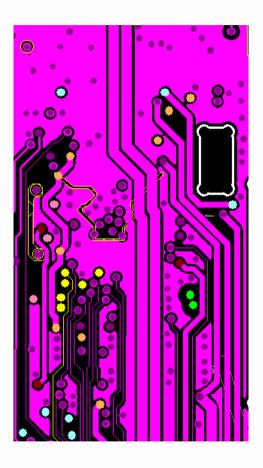

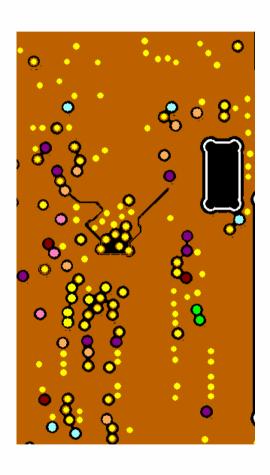

# MT6516 reference phone PCB layer define

| Layer<br>No.                         | Name     | Define   | Material    |            | Suggestion      | Die.<br>Con. | suggest<br>thickness(mil) | Via      |

|--------------------------------------|----------|----------|-------------|------------|-----------------|--------------|---------------------------|----------|

|                                      |          |          | SolderMask  | SolderMask |                 |              | 0.4                       |          |

|                                      |          |          | Add Plating | plating    |                 |              |                           |          |

| 1                                    | COMP(L1) | RF Trace | Copper foil | 0.5 oz     | H oz+plating    |              | 1.4                       | <b>†</b> |

|                                      |          |          |             | PP         | PP 1080 65%     | 4.3          | 2.82                      |          |

| 2                                    | L2       | Signal   | Copper foil | 1.0 oz     | 0.50 oz+plating |              | 1.3                       | 1        |

|                                      |          |          |             | CORE       | PP 1080 65%     | 4.3          | 2.82                      |          |

| 3                                    | L3       | GND      | Copper foil | 1.0 oz     | Copper 1.0 oz   |              | 1.3                       |          |

|                                      |          |          |             | PP         | FR-4 Core 4mil  | 4.3          | 4                         |          |

| 4                                    | L4       | RF Trace | Copper foil | 1.0 oz     | Copper 1.0 oz   |              | 1.3                       |          |

|                                      |          |          |             | CORE       | PP 7628 50%     | 4.3          | 8.38                      |          |

| 5                                    | L5       | GND      | Copper foil | 1.0 oz     | Copper 1.0 oz   |              | 1.3                       |          |

|                                      |          |          |             | PP         | FR-4 Core 4mil  | 4.3          | 4                         |          |

| 6                                    | L6       | Signal   | Copper foil | 1.0 oz     | Copper 1.0 oz   |              | 1.3                       |          |

|                                      |          |          |             | CORE       | PP 1080 65%     | 4.3          | 2.82                      |          |

| 7                                    | L7       | Signal   | Copper foil | 1.0 oz     | 0.50 oz+plating |              | 1.3                       | + +      |

|                                      |          |          |             | PP         | PP 1080 65%     | 4.3          | 2.82                      |          |

| 8                                    | SOLD(L8) | RF Trace | Copper foil | 0.5 oz     |                 |              |                           |          |

|                                      |          |          | Add Plating | plating    | H oz+plating    |              | 1.4                       | <b>+</b> |

|                                      |          |          | SolderMask  | SolderMask |                 |              | 0.4                       |          |

| Board<br>Thickness<br>=1.00mm<br>+/- |          |          |             |            |                 |              | 39.06                     |          |

| 10%mm                                |          |          |             |            |                 |              |                           |          |

# MEDIATEK

# MT6326 PMIC Design Notice

Copyright © MediaTek Inc. All rights reserved.

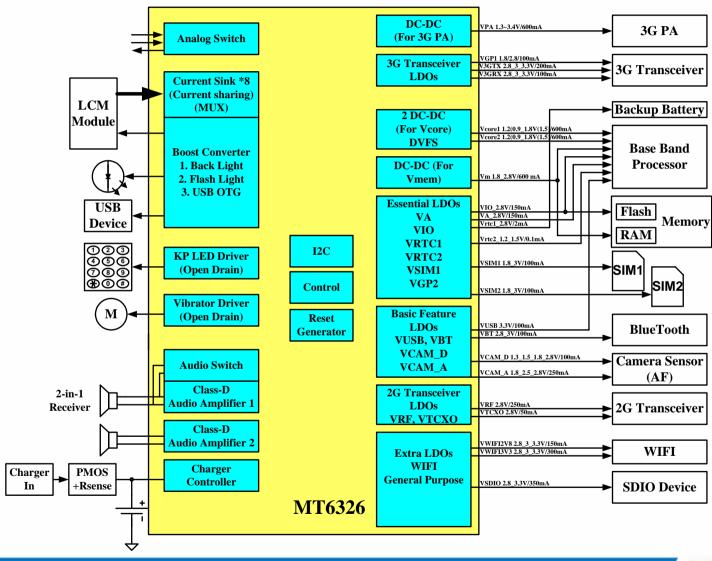

### **MT6326 PMIC**

# MT6326 PMIC LDO

| Regulator  | Output Voltage                      | <b>Output Current</b> | <b>Output Components</b> | Notes                                                             |

|------------|-------------------------------------|-----------------------|--------------------------|-------------------------------------------------------------------|

| VCORE      | 0.9~1.35<br>1.8                     | 600                   | 2.2uH + 4.7uF            | Max. output current = $100$ mA when set to $< 1.1$ V              |

| VCORE 2    | 0.9~1.35<br>1.8                     | 600                   | 2.2uH + 4.7uF            | Max. output current = $100$ mA when set to $< 1.1$ V              |

| VM         | 1.8<br>2.8                          | 600                   | 2.2uH + 4.7uF            | Max. output current = $450$ mA when set to $2.8$ V                |

| V3GPA      | 1.3~3.4                             | 600                   | 2.2uH + 4.7uF            | VBAT should keep 600mV higher than V3GPA to keep good regulation. |

| V3GTX      | 2.5/2.8/3/3.3                       | 200                   | 4.7uF                    |                                                                   |

| V3GRX      | 2.5/2.8/3/3.3                       | 100                   | 4.7uF                    |                                                                   |

| VRF        | 2.8                                 | 250                   | 4.7uF                    |                                                                   |

| VTCXO      | 2.8                                 | 50                    | 1uF                      |                                                                   |

| VA         | 2.8                                 | 150                   | 4.7uF                    | For AVDD, FM power requirement                                    |

| VCAMA      | 1.5/1.8/2.5/2.8                     | 250                   | 4.7uF                    |                                                                   |

| VWIFI3V3   | 2.5/2.8/3/3.3                       | 300                   | 4.7uF                    |                                                                   |

| VWIFI2V8   | 2.5/2.8/3/3.3                       | 150                   | 4.7uF                    |                                                                   |

| VIO        | 2.8                                 | 150                   | 1 uF                     | For VDD and peripheral I/O requirement                            |

| VSIM       | 1.8/3.0                             | 100                   | 1uF                      |                                                                   |

| VUSB       | 3.3                                 | 100                   | 1uF                      |                                                                   |

| VBT        | 1.3/1.5/1.8/2.5/2.8/3.0/3.3         | 100                   | 1uF                      |                                                                   |

| VCAMD      | 1.3/1.5/1.8/2.5/2.8/3.0/3.3         | 100                   | 1uF                      |                                                                   |

| VSDIO      | 2.8/3                               | 300                   | 4.7uF                    |                                                                   |

| VGP1       | 1.3/1.5/1.8/2.5/2.8/3.0             | 100                   | 1uF                      |                                                                   |

| VGP2       | 1.3/1.5/ <b>1.8</b> /2.5<br>2.8/3.0 | 100                   | 1uF                      |                                                                   |

| VRTC       | 1.5/1.2                             | 0.1                   | 1uF                      |                                                                   |

| BAT_BACKUP | 2.8                                 | 2                     | 1uF                      | Backup battery                                                    |

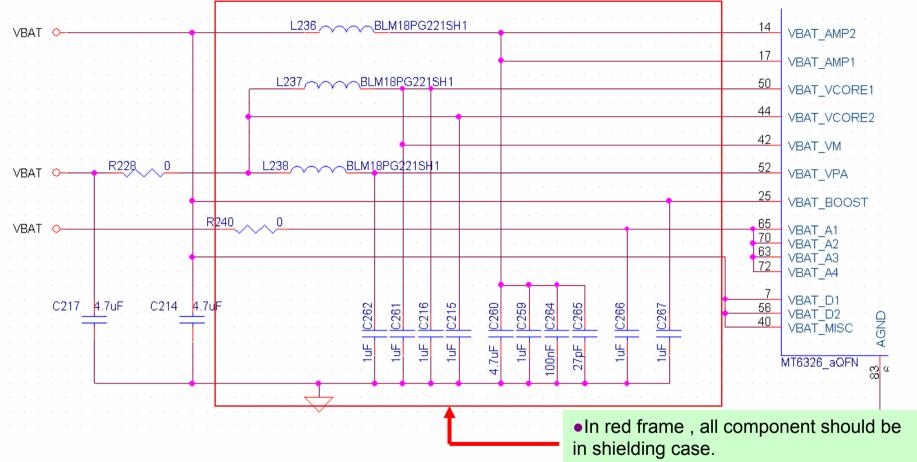

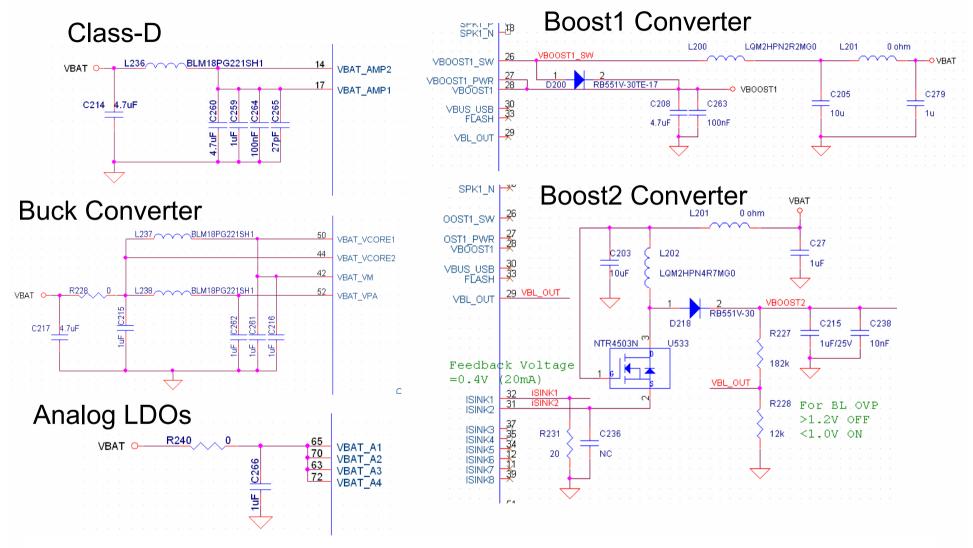

# **VBAT Input Filter**

- VBAT input should reserve enough filter to prevent interference to RF performance.

- All above component should be as close to MT6326 IC as possible

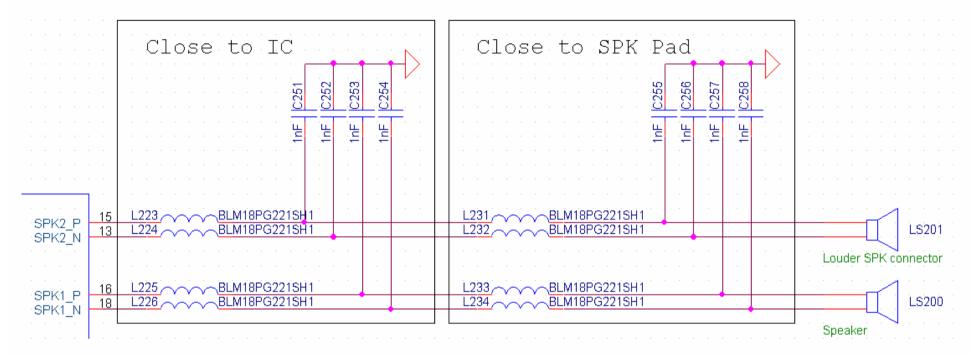

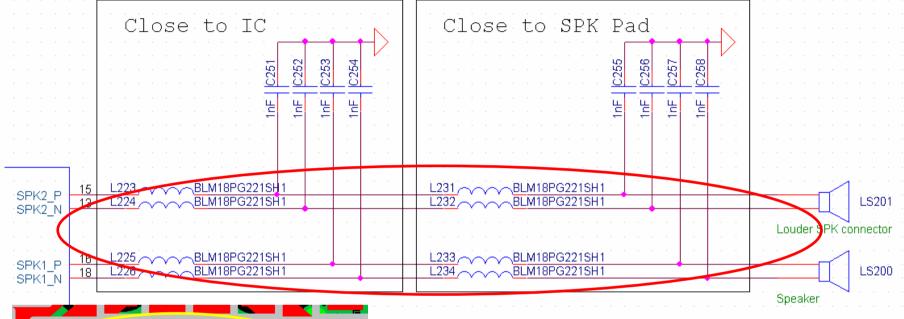

# **Class-D Audio Amplifier Output Filter**

- Reserve 2 stage filter at output stage of Class-D to prevent interference to RF performance.

- 1st stage filter should be close to IC, 2nd stage filter should be close to loud speaker.

- All the traces from IC to 2<sup>nd</sup> stage filter should not exposed to prevent interference to RF performance.

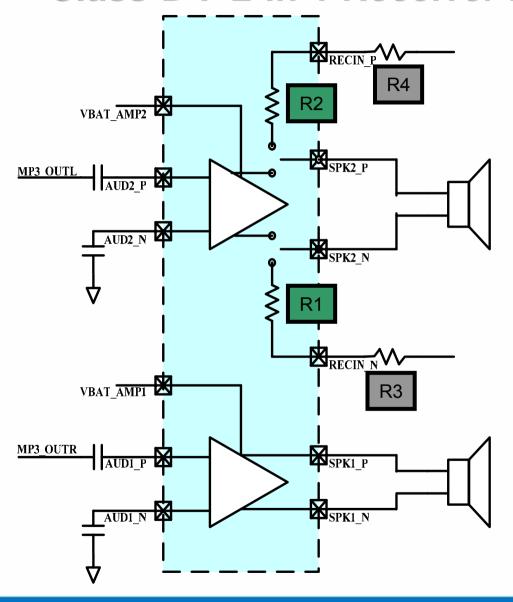

### Class-D: 2-in-1 Receiver Function

- MT6326 has 2 in 1 receiver function, when use external amplifier, must connect RECIN\_P and RECIN\_N.

- The typical value of R1 and R2 are 20 ohm each, and suggest R3 and R4 to be 4 ohm (32–20–8=4)

- Due to value variation of R1 and R2 are higher, so maybe suffer audio volume.

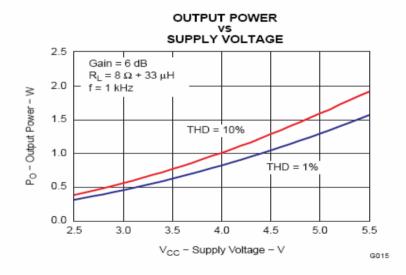

# **Class-D: Audio Amplifier Power Output**

|                            | MT6326 Class-D Ampilifer                        | TI TPA2016D2 Class-D Ampilifer |                                                 |        |

|----------------------------|-------------------------------------------------|--------------------------------|-------------------------------------------------|--------|

|                            | THD+N = $10\%$ , VDD = $4.2$ V, RL = $8 \Omega$ | 1.2 W                          | THD+N = $10\%$ , VDD = $5$ V, RL = $8\Omega$    | 1.72 W |

| Pomax Maximum output power | THD+N = 10%, VDD = 3.3 V, RL = 8 $\Omega$       | 720 mW                         | THD+N = $10\%$ , VDD = $3.6$ V, RL = $8 \Omega$ | 750 mW |

|                            | THD+N = 1%, VDD = 4.2 V, RL = 8 Ω               | 1 W                            | THD+N = 1%, VDD = 5 V, RL = 8 $\Omega$          | 1.4 W  |

|                            | THD+N = $1\%$ , VDD = $3.3$ V, RL = $8 \Omega$  | 600 mVV                        | THD+N = $1\%$ , VDD = $3.6$ V, RL = $8\Omega$   | 630 mW |

• Although MT6326 class-D power output is 1W at 8  $\Omega$ , because congenital power source limitation is 4.2V from VBAT, but compare with other discrete amplifiers, MT6326 equal other amplifier in performance.

TI Poutput Profile

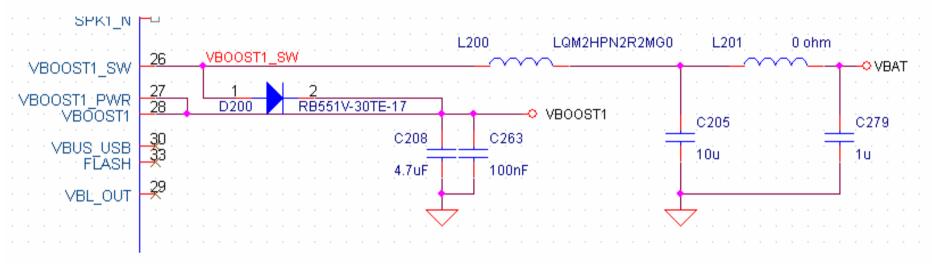

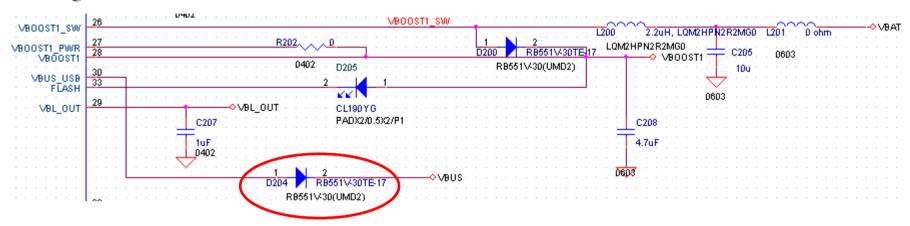

# Boost1 For Parallel Backlight LCM or other 5 Maintial B requirement

- Reserve filter at input/output to prevent interference to RF performance.

- L200/L201/C205/C279 should be in shield case and close near MT6326

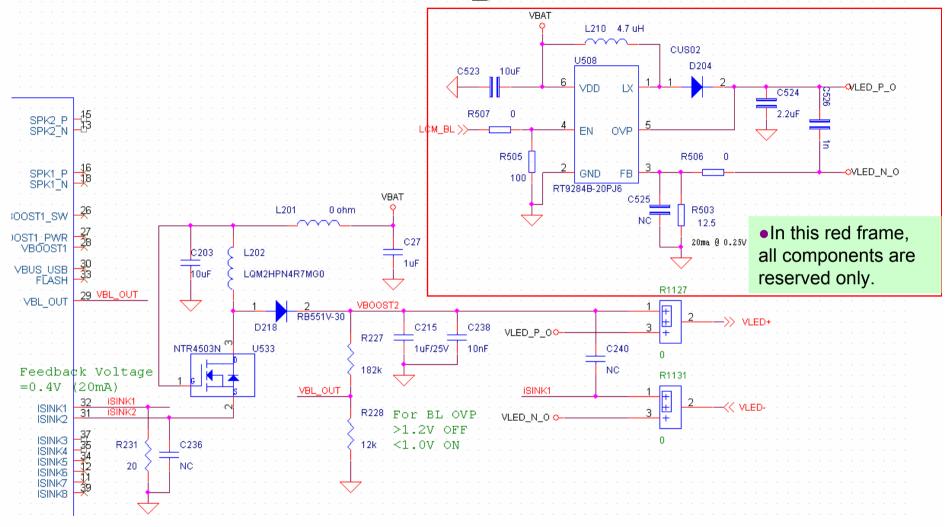

### **Boost2 For Serial Backlight LCM**

Reserve discrete B/L driver to prevent any improper design causing interference to RF performance.

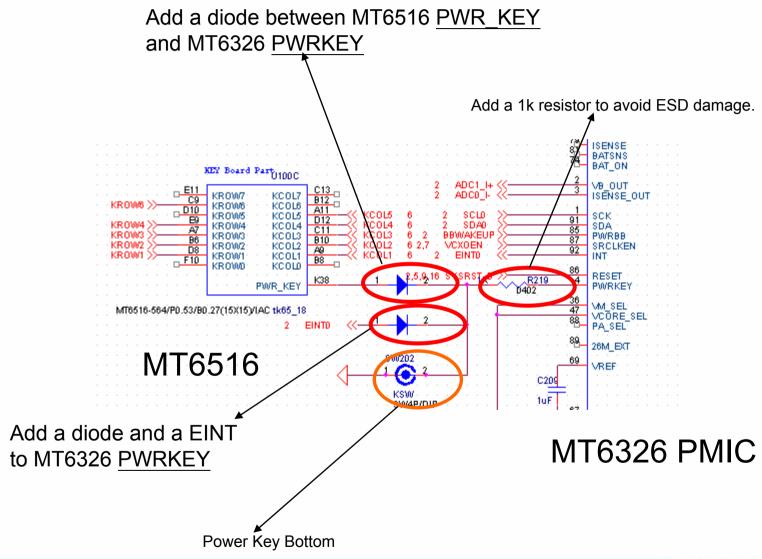

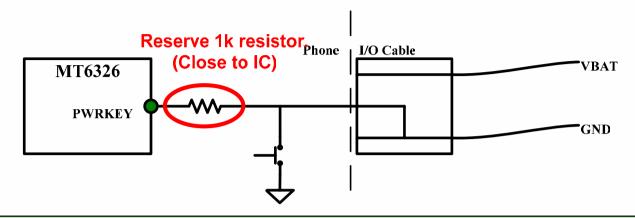

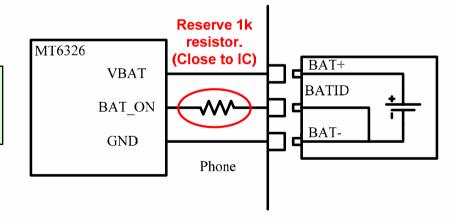

# IC Protection: PWRKEY and BAT\_ON

Please reserve 1k resistor on phone PCB to protect **PWRKEY** no matter if PWRKEY connect to any I/O connector or not.

Please reserve 1k resistor on phone PCB to protect **BAT\_ON** pin if BAT\_ON is used to detect battery.

### **IC Protection: VBAT**

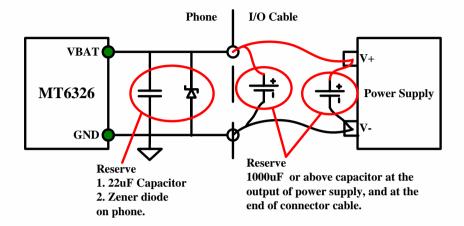

MT6326 has lower VBAT voltage rating. (Max. 4.3V.) Some protection should reserve to prevent the damage by voltage surge.

- •Design notice in Phone side:

- 1. At least 22uF capacitor.

- 2. Add Zener diode (5.1V) to protect the IC against low frequency voltage surge. Put it between battery connector and MT6326.

Notice: If using IO connector or test point to supply VBAT for download, manufacture, or repair, should let VBAT trace passing zener diode and 22uF capacitor before entering IC. Notice: Using 5.1V zener will introduce some leakage when VBAT = 4.2V.

•Design notice in Power Supply side:

Add 1000uF (or above) capacitor at the output of the power supply to reduce the voltage bounce caused by long power cable. And the power cable should be as short as possible. Also add 1000uF (or above) capacitor at the end of power cable (near phone side).

### **IC Protection: CHRIN**

|                    | MT6305<br>/MT6318 | MT6223/35/38<br>/MT6326 | External OVP/OCP |

|--------------------|-------------------|-------------------------|------------------|

| Max. Charger Input | 15V               | <b>9V</b>               | 30V              |

| Charger OVP Point  | 9V                | <b>7V</b>               | 6.8V             |

#### **External OVP/OCP:** OVP/OCP Qualified Vendor: R201 NC TI - BQ24314 U202 F201 TO CHRIN CHRIN OUT VCHG O-FUSE(1A 0603) C205 Notice: VSS ILIM **K**205 1uF NC **VBAT** You can get better charger protection by /CE /fault using external OVP/OCP device. BQ24316 **VBAT** R202 220K

# IC Protection: OVP + Charger

|                    | MT6305<br>/MT6318 | MT6223/35/38<br>/MT6326 | External OVP/OCP                 |

|--------------------|-------------------|-------------------------|----------------------------------|

| Max. Charger Input | 15V               | <b>9V</b>               | 30V                              |

| Charger OVP Point  | 9V                | <b>7V</b>               | 6.17V(APL3206)<br>6.8V(APL3206A) |

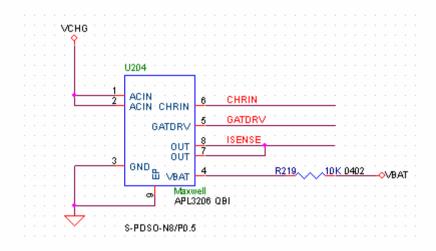

#### **External OVP + Charger:**

OVP/OCP + Charger Qualified Vendor :

ANPEC - APL3206 QBI

#### Notice:

You can get better charger protection by using external OVP/OCP device.

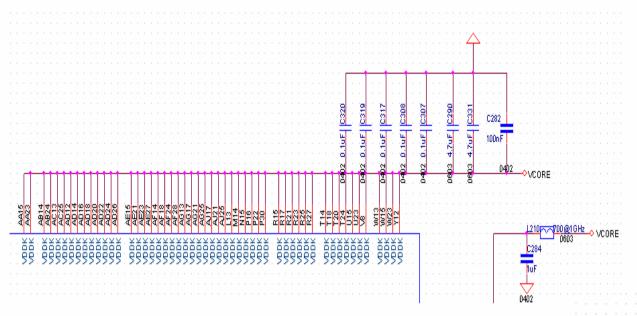

# **Bypass Capacitor: Vcore and VM**

#### Confidential B

AVDD12

AVDD12

AVDD12

AVDD12

AVDD12

AVDD12

AVDD12

AVDD14

AVDD14

AVDD15

Reserve enough bypass capacitors both at Vcore and VM to obtain good system stability.

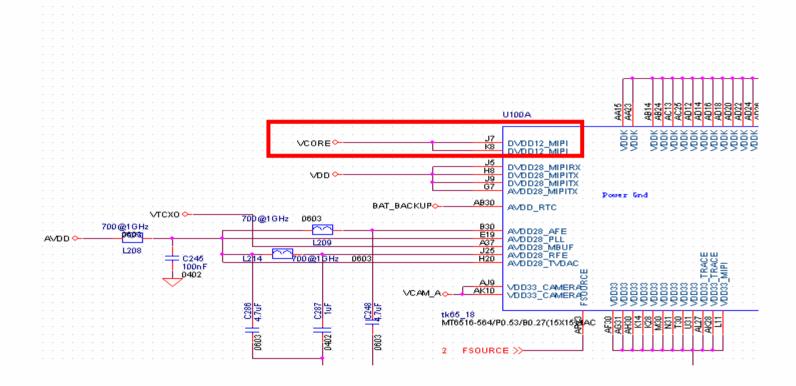

## **DVDD12\_MIPI** Power Connection

MT6326 Vcore1 default is 1.3V, and MIPI\_1.2V power spec. is 1.1~1.3V, so if need to use MIPI could connect Vcore2(if not used). Besides, must add external LDO for MIPI\_1.2V.

# **Bypass Capacitor: Layout Rule For Vcore**

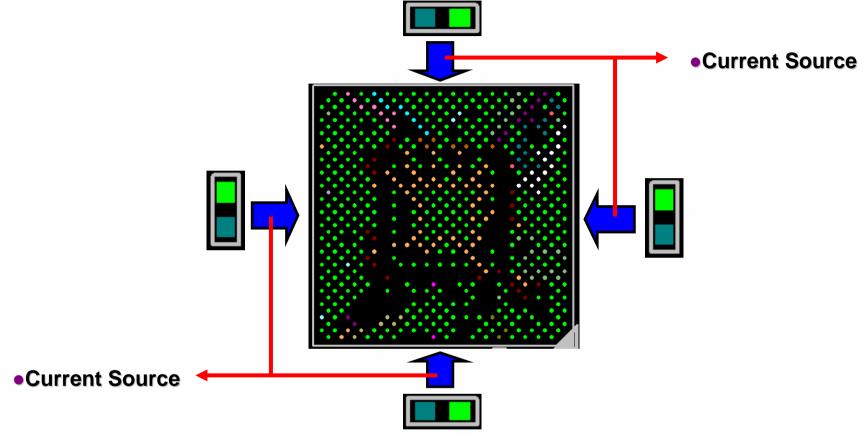

Due to MT6516 have many Vcore (VDDK) balls, and these balls scatter around package of MT6516. Please put bypass capacitor around MT6516 to increase system reliably.

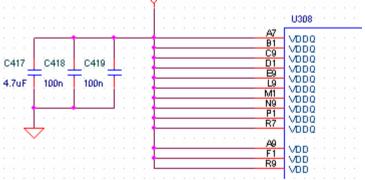

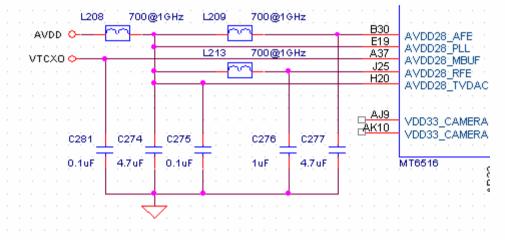

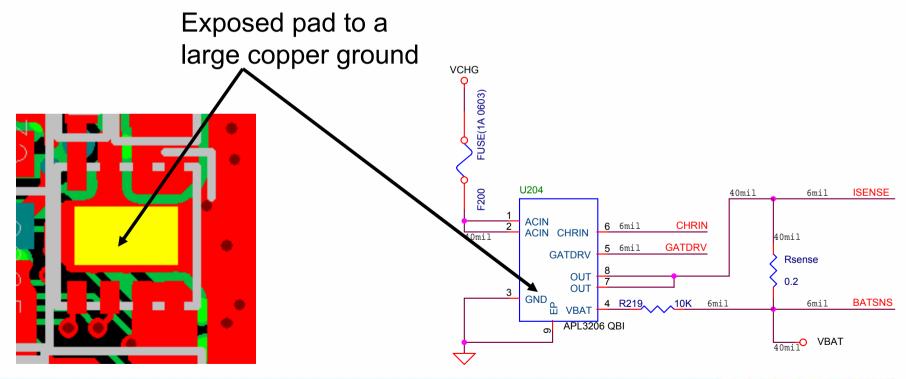

## **Bypass Capacitor: AVDD and VDD**

- Reserve required input filter for ABB as specified in left schematics.

- AVDD28\_MBUF suggest to connect to VTCXO.

Reserve 1uF for I/O power input.

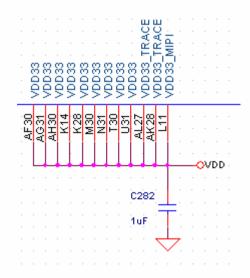

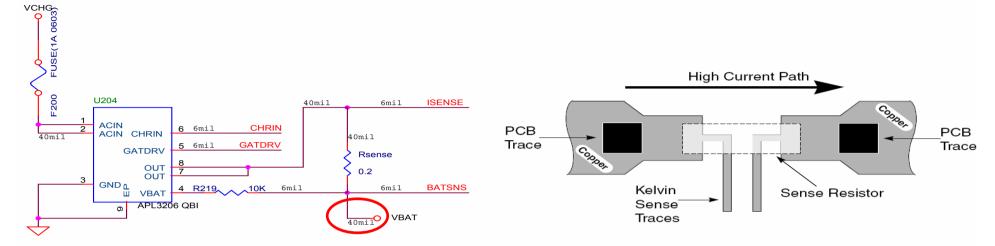

## **Layout Notice: Charging Path**

- Charging related component (U204, Rsense, R219) should be close to battery connector.

- Minimum trace width are marked on the schematics above.

- ISENSE and BATSNS should be connected as the figure above.

- The trace from Rsense to battery connector (Marked in Red) should not share with other VBAT traces.

- ISENSE/BATSNS should be routed as differential traces which are away from noisy signals.

### **Layout Notice: Charger OVP IC**

- The exposed pad of the charger OVP IC should connect to a large copper ground plane to get good thermal performance.

- The exposed pad should has at least 6 GND via connecting to inner layer.

#### **Layout Notice: VBAT Traces**

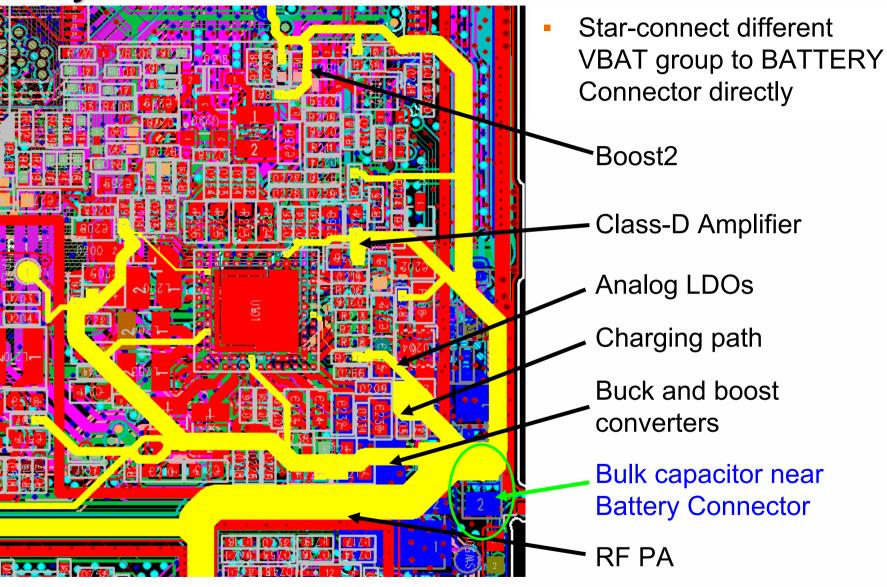

The VBAT for the 5 blocks show above (Class-D, Buck converter, Boost1, Boost2 converter and Analog LDOs) should star-connect to the bulk capacitor near battery connector.

#### **Layout Notice: VBAT Traces**

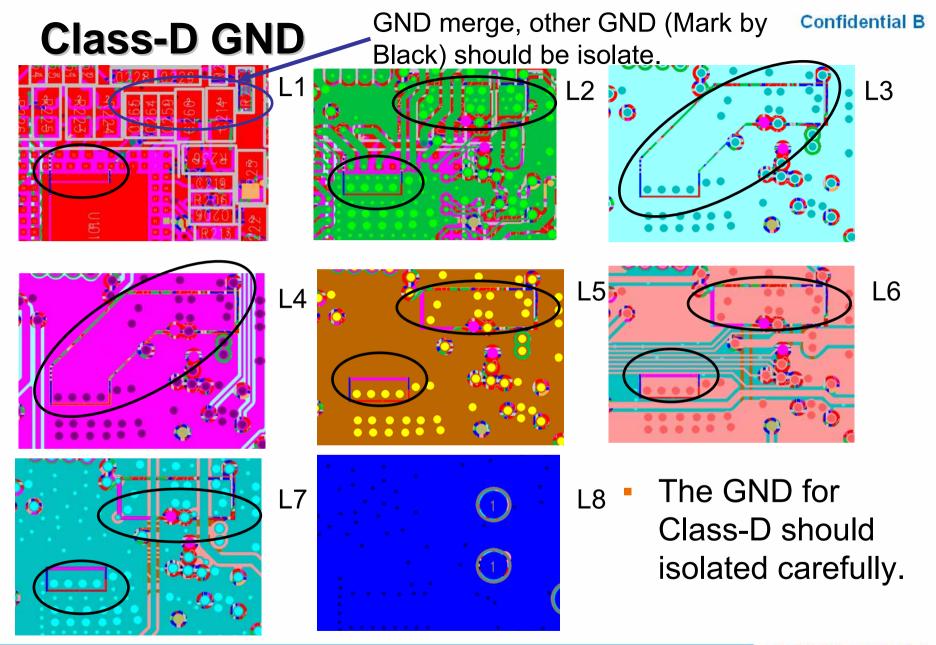

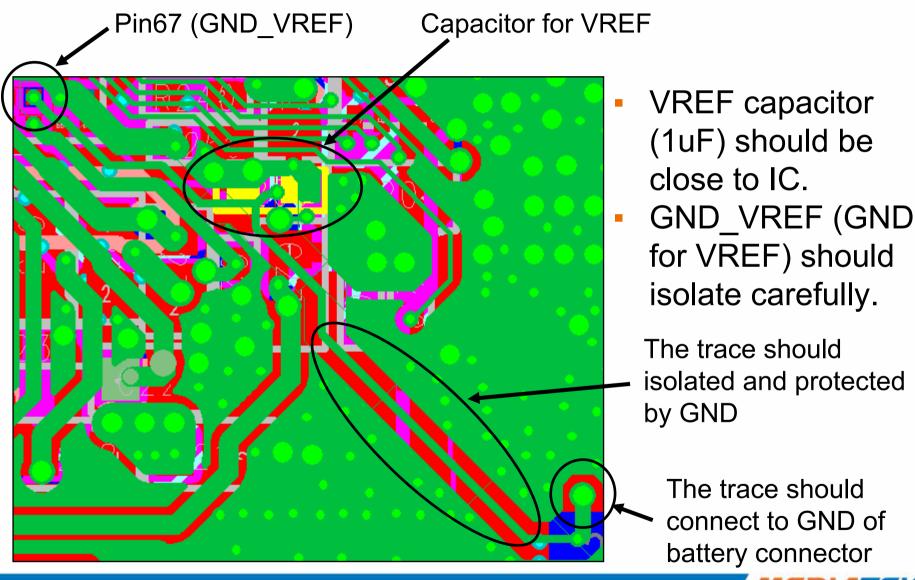

### **Layout Notice: GND\_VREF Traces**

## **Layout Notice: Class-D Output**

- 2 2 2 2 1 1 1 1 1 9 17 15 13 1 9 17 15 13 10 8 16 14 12 10 8

- The output trace (Marked in above schematics) should be differential, and protected by GND.

- 1st filter should be as close to IC as possible. (As the left figure showed.)

- The trace width should be

- 8 ohm speaker: 25 mil.

- 4 ohm speaker: 40 mil.

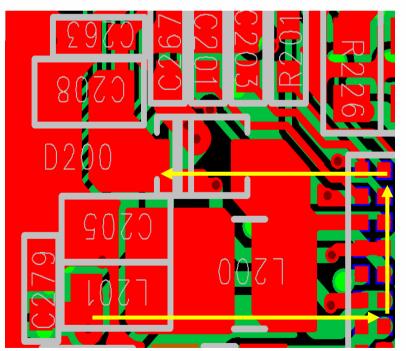

## **Layout Notice: Boost1**

- Components should be as close to IC as possible.

- L200/D200/L201/C205/D200/C208 should be close and parallel to each other.

- The direction of L200/D200 should arrange as the arrowhead in left figure.

- Must add D204 to prevent feedback of VBUS when turn off boost1.

# MEDIATEK

# MT6516 Design Notice (Audio)

Copyright © MediaTek Inc. All rights reserved.

#### **Outline**

- Analog gain setting

- RC value

- PCB layout

- Audio feature

- MP3 decoder

- 3D surround effect

- EQ 2.0

- Audio AGC

- Audio Compensation Filter

- For audio features, please refer to

- L1\_Audio\_Design\_and\_Interface.pdf

- Audio\_Post-Processing\_Interface\_V1.13.pdf

- Audio Customization v1.0.pdf

#### **Audio Block Diagram Audio Buffer** Audio Amp-L Audio LCH-DAC Audio Signal AU\_MOUTR Audio RCH-DAC Audio Amp-R AU\_FMINL FM/AM radio Stereo-to-Mono chip AU\_FMINR Voice Signal Voice Buffer Voice DAC Voice Amp-1 AU\_DUT0\_P Microphone PGA AU\_OUTO\_N AU\_VIN0\_P PGA Voice Signal AU\_VIN0\_N Voice ADC AU\_VIN1\_N Copyri AU\_VIN1\_P

#### **Audio Buffer Gain**

- Analog gain setting

- LoudSPK mode

- Audio buffer

- -112 = -1dB

- -Positive gain results distortion

- External amplifier

- -increasing external amplifier gain for louder volume

- Earphone mode

- Audio buffer

- -112 = -1dB

- -Positive gain results distortion

- External RC trade-off

| setting in engineering mode | audio<br>Buffer<br>[dB] | voice<br>Buffer<br>[dB] |

|-----------------------------|-------------------------|-------------------------|

| 240                         | 23                      | 8                       |

| 224                         | 20                      | 6                       |

| 208                         | 17                      | 4                       |

| 192                         | 14                      | 2                       |

| 176                         | 11                      | 0                       |

| 160                         | 8                       | -2                      |

| 144                         | 5                       | -2<br>-4                |

| 128                         | 2                       | -6                      |

| 112                         | -1                      | -8                      |

| 96                          | -4                      | -10                     |

| 80                          | -7                      | -12                     |

| 64                          | -10                     | -14                     |

| 48                          | -13                     | -16                     |

| 32                          | -16                     | -18                     |

| 16                          | -19                     | -20                     |

| 0                           | -22                     | -22                     |

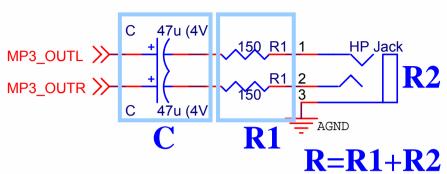

#### **External RC value**

- RC value on mp3\_out path

- 1) Bandwidth:  $f_c = \frac{1}{2\pi RC}$

- 2) Amplitude degradation: *amplitude*  $[dB] = 20 \log \frac{R2}{R1 + R2}$

- 3) Larger resistance, better bass, smaller volume;

- 4) Larger capacitance, better bass, higher cost, larger PCB area.

- 5) Pout < Earphone speaker rated power  $P_{out} = \frac{(V_{rms})^2}{R^2}$

- 6) example:

- (R1, C, Fc, Amplitude)

- (100ohm, 47uF, 25.65Hz, -12.3dB)

#### **External RC value**

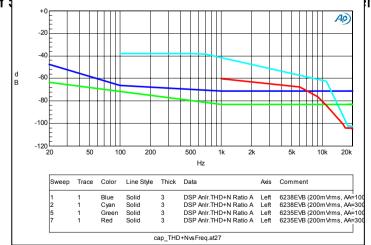

- Different types of capacitors have different distortion.

- distortion: Tantalum cap. > MLCC X5R > MLCC Y5V

- Don't use MLCC Y5V in audio path/ mic0/ FM\_IN

- Capacitors' THD+N vs. Frequency are showed as below:

- green: X5R (+/-10%); Audio Precision Analyzer Rin=100kohm

- red: X5R (+/-10%); Audio Precision Analyzer Rin=100kphm

- blue: Y5V (+80%, -20%); Audio Precision Analyzer Rin=300ohm

• cyan: Y

#### **External RC value**

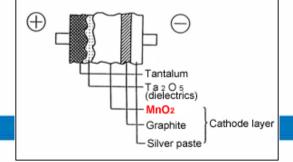

- Tantalum capacitor

- Can't be operated under reverse bias,

- HP EINT can't be on earphone path.

- Permissible reverse voltage:

| Ambient Temperature         | 25°C                          | 55°C      | 85°C      | 125°C      |

|-----------------------------|-------------------------------|-----------|-----------|------------|

| Permissible Reverse Voltage | R.V. × 10%                    | R.V. × 6% | R.V. × 3% | D 37 × 10/ |

| Termissione reverse voltage | or 0.5V whichever is greater. |           |           | R.V. × 1%  |

- The reason of damage by reverse voltage

- Reverse voltage will damage Ta2O5,

- After Ta2O5 is broken, there is large current passed through

tantalum capacitor.

#### **External RC value**

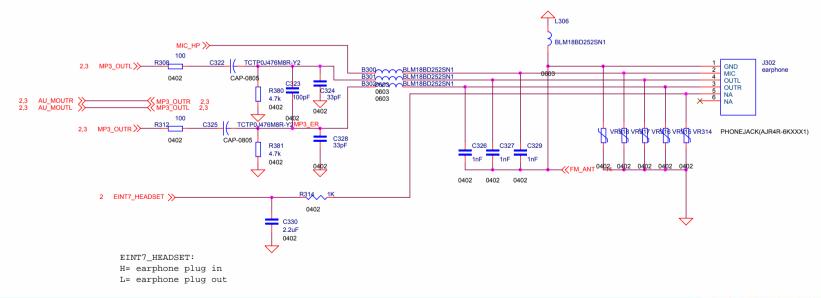

- HP EINT suggestion

- 18-pin I/O

- An extra pin for HP EINT and accessory need a pull-low resister.

- 6-pin earphone jack

- Two extra pull-low resistors on CH-L/R

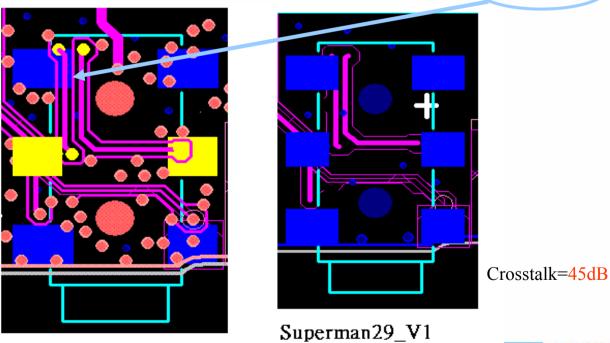

#### **Audio Traces**

- Crosstalk issue

- avoid CH-L and CH-R's signal interfering to each other

- (1) PCB layout

- protected audio R & L stereo trace by GND separately.

Copyright © MediaTek

Crosstalk=70dB

Superman29\_V2

#### **Audio Traces**

- Crosstalk issue

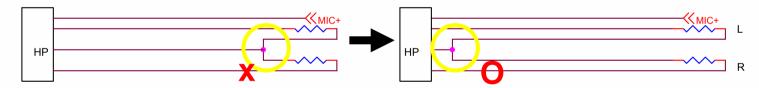

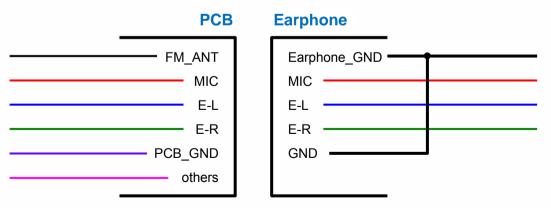

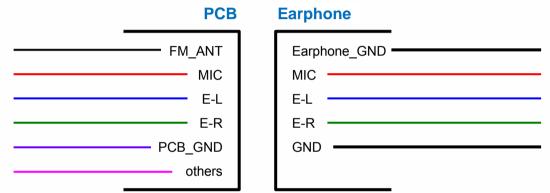

- (2) earphone accessory:

- Separated GND of CH-L and CH-R.

- connect the GND of CH-L and CH-R at the end of earphone jack.

Not connect the GND at earphone microphone.

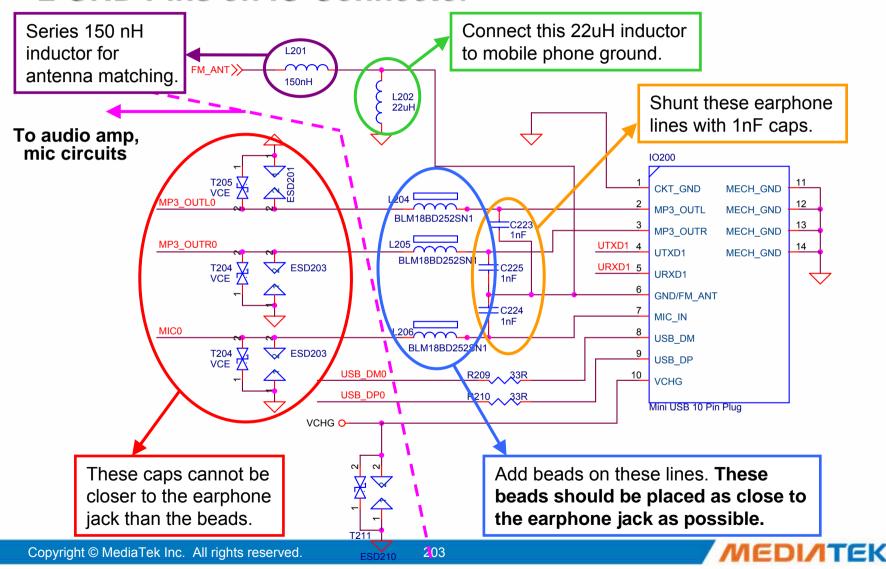

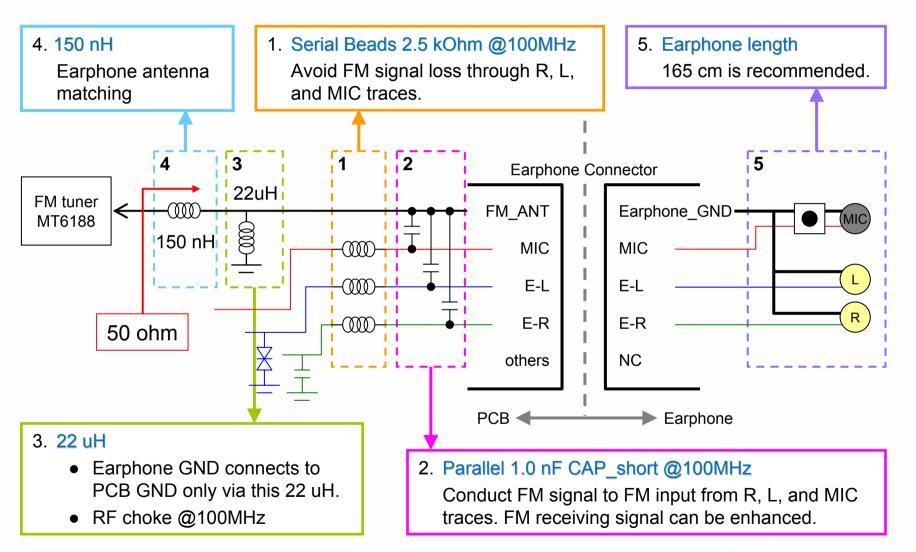

- (3) The bead at FM ANT on earphone path may degrade crosstalk about 15dB.

- Choose bead with low DRC bead and good THD+N

- It is a trade-off between FM feature and crosstalk performance.

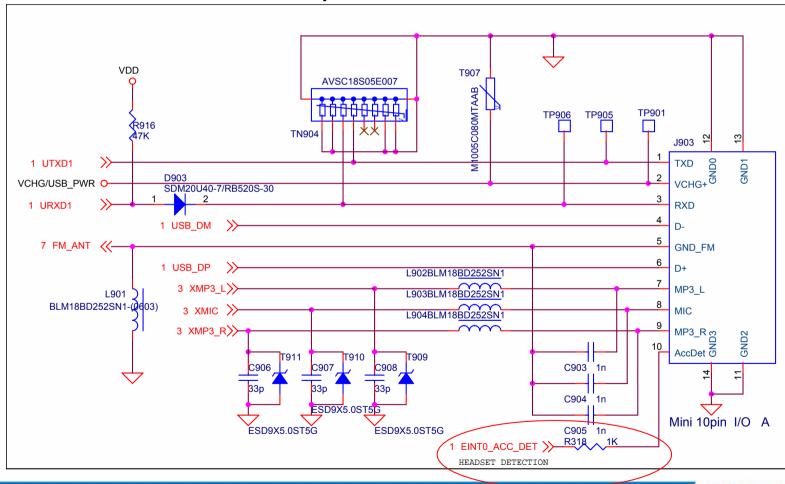

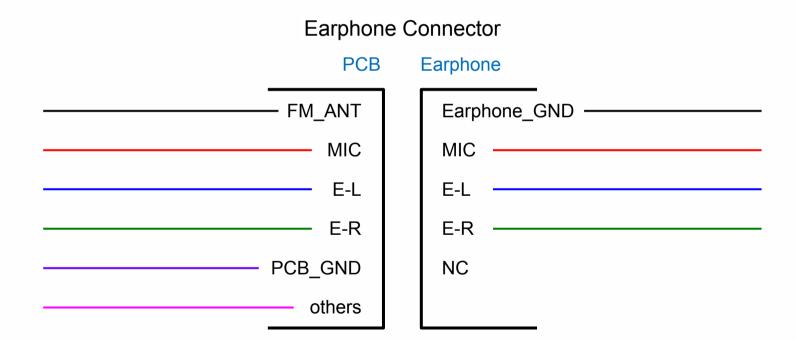

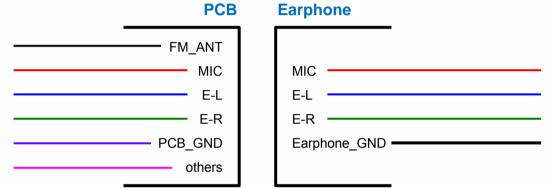

# I/O connector (10pins)

UART + USB + Earphone

## Case Study (1)

#### Audio pop noise

- LoudSPK mode

- Tuning external audio amplifier ON/OFF delay time

- mp3\_outL/R to external amplifier input must add coupling capacitor to avoid voltage drop.

- Earphone mode

- Turn on de-pop function by software

- Tantalum capacitor +/- reverse mounting.

## Case Study (2)

#### Loudness without distortion

- LoudSPK mode

- Audio buffer gain <112</li>

- Increase external audio amplifier gain

- Earphone mode

- Audio buffer gain <112</li>

- decrease resistance on earphone path

- Increase capacitance for good bandwidth

- Microphone PGA

- uplink speech volume

- nvram\_default\_audio.c: #define GAIN\_NOR\_MIC\_VOL3

- Engineering mode: audio, normal mode. microphone, volume3

- sound recorder/video recording volume

- nvram default audio.c: #define GAIN NOR MIC VOL4

- Engineering mode: audio, normal mode. microphone, volume4

- FM recorded file playback

- Increase FM\_record\_PGA if FM playback volume is small.

- mcu\1audio\afe2.c: #define FM\_RADIO\_RECORDING\_VOLUME

# MEDIATEK

# MT6516 Design Notice (Speech)

Copyright © MediaTek Inc. All rights reserved.

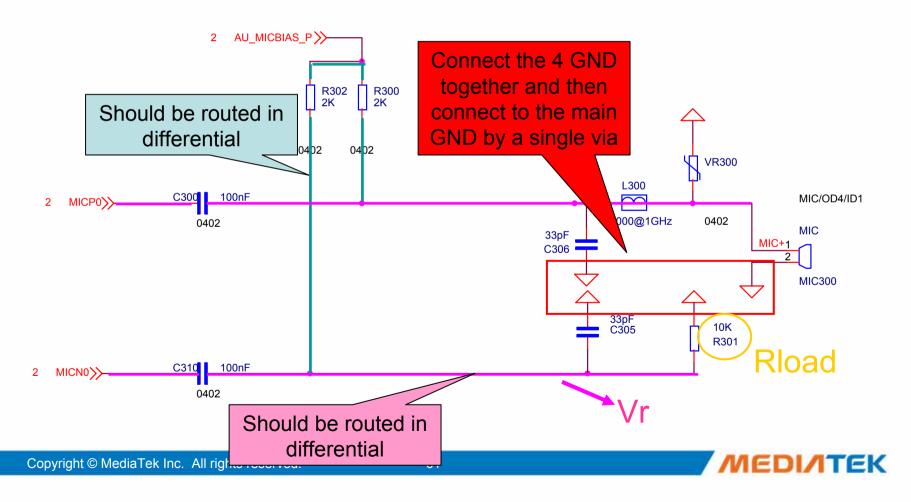

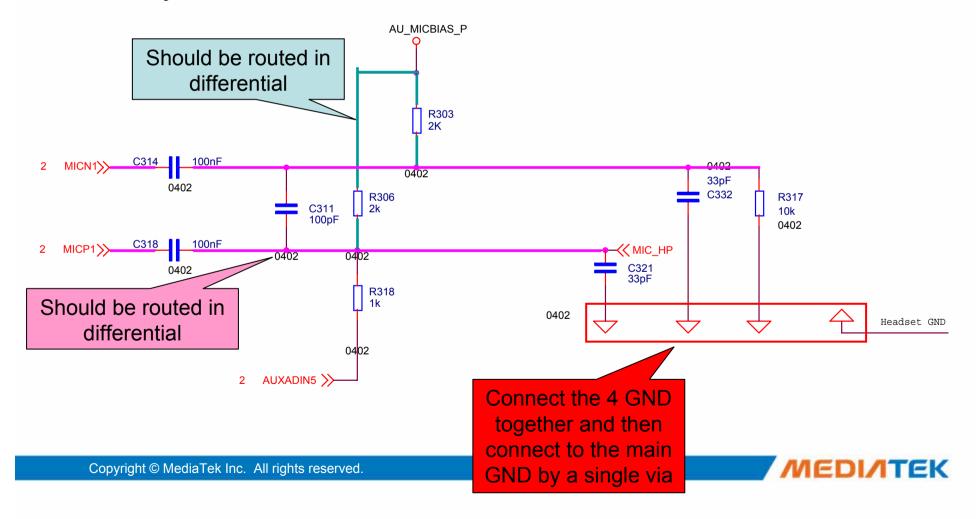

- Advantage

- 10uf capacitor is not needed any more

- Less passive components are needed

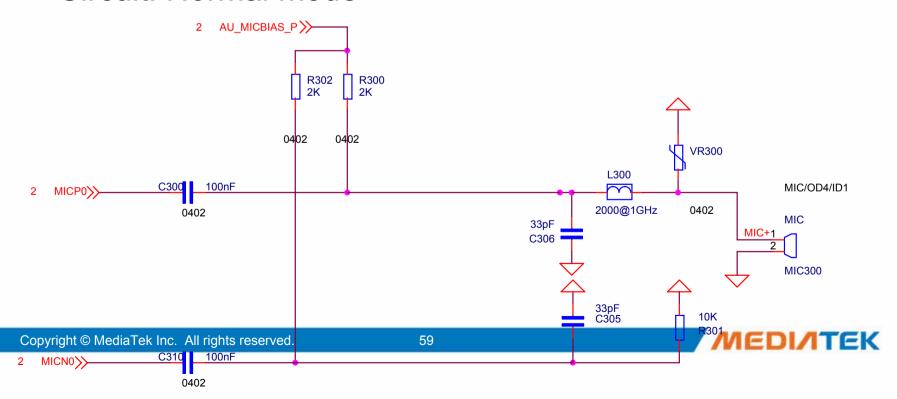

- Circuit: Normal mode

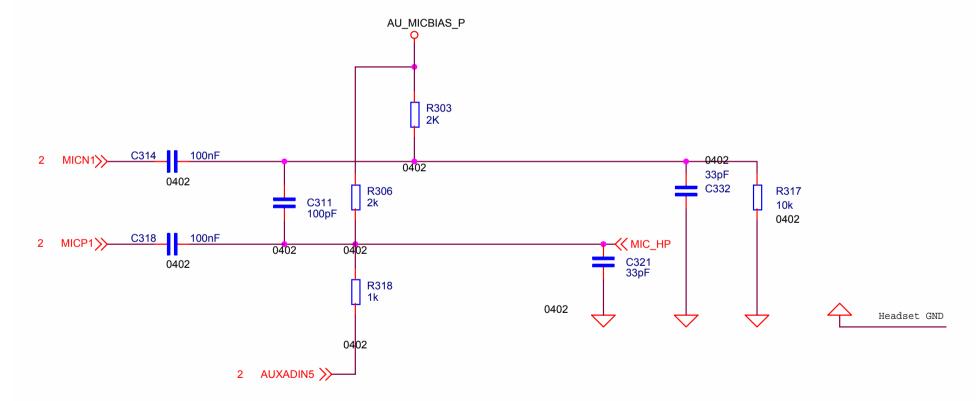

Circuit: Headset mode

Layout consideration-Normal mode

Layout consideration-Headset mode

# **How to Optimized Rload**

- The Rload can be calculated by the follow procedure

- Measure the voltage on the microphone MIC\_P in a quite environment

- Select a Rload to let Vr has almost the same voltage as MIC\_P

# MEDIATEK

# **MT6516 Camera Design Notice**

$\label{local_constraints} \mbox{Copyright} @ \mbox{MediaTek Inc. All rights reserved}.$

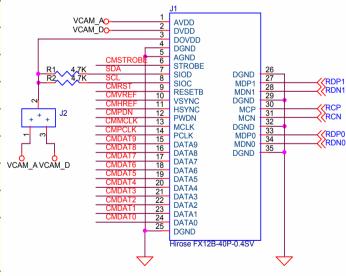

# Camera Design Note – Parallel Interface

- All camera pins are dedicated

- Layout notice

- CMMCLK, CMPCLK need to be well shielded by GND plane

- BB side power level

- VDD33\_CAMERA (AJ9, AK10) = Camera side IO level DOVDD

| MT6516 (Pin definition) |                                            | Camera side   |

|-------------------------|--------------------------------------------|---------------|

| CMVREF                  | AH8                                        | VSYNC         |

| CMHREF                  | AT2                                        | HSYNC         |

| CMPCLK                  | AG9                                        | PCLK          |

| CMMCLK                  | AR3                                        | MCLK          |

| SDA1                    | AP2                                        | SIOD          |

| SCL1                    | AG5                                        | SIOC          |

| CMRST                   | AJ7                                        | RESETB        |

| CMPDN                   | AM4                                        | PWDN          |

| CMDAT0~CMDAT9           | AV2,AL9,AT4,AM8,AU3<br>AN7,AN5,AK8,AP4,AL7 | DATA0 ~ DATA9 |

| CAM_STROBE              | AN3                                        | STROBE        |

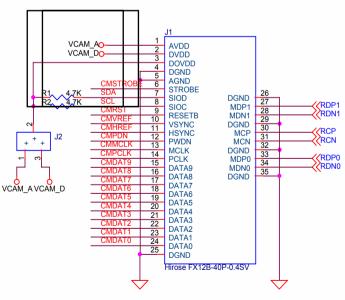

## Camera Design Note – MIPI (CSI-2) Interface

- All MIPI DSI pins are dedicated that connect from BB to LCM

- 1 CLK Lane + 2 Data Lanes

- BB side TVRT (pin G5) connect 1.8K 1% resistor to GND and close to BB

- Layout notice

- All signal pairs need to 50ohm impedance matching for single end and 100ohm for differential

- All signal length need be equal and well shielded by GND plane

- BB side power level

- VDD33 CAMERA (AJ9, AK10) = Camera side IO level DOVDD

- DVDD12 MIPI (J7, K8) connect to VCORE(1.2V)

- DVDD28\_MIPITX (H8, J9), DVDD28\_MIPIRX(J5), AVDD28\_MIPITX (G7), and VDD33\_MIPI (L11) connect to VDD (2.8V)

| MT6516 (Pin definition) |     | Camera side |

|-------------------------|-----|-------------|

| RDP1                    | H2  | MDP1        |

| RDN1                    | G1  | MDN1        |

| RCP                     | G3  | MCP         |

| RCN                     | F2  | MCN         |

| RDP0                    | E3  | MDP0        |

| RDN0                    | E1  | MDN0        |

| CMRST                   | AJ7 | RESETB      |

| CMPDN                   | AM4 | PWDN        |

| CAM_STROBE              | AN3 | STROBE      |

# MEDIATEK

# MT6516 LCM Design Notice

Copyright © MediaTek Inc. All rights reserved.

# **Display Interfaces**

- Various Interface Support

- 8080 host IF (MIPI DBI)

- 8/9/16/32-bit Serial IF

- RGB interface (MIPI DPI)

- MIPI DSI interface

- High performance LCD controller enable wide range of display resolution

- Landscape or Portrait mode.

- From 128x96(SubQCIF) ~ 852x480(WVGA)

- Advance color processing

- Embedded LCD Gamma correction table.

- Color correction matrix.

- true color support.

- Contrast, brightness adjustment.

- 6 overlay layers with per-pixel alpha channel and gamma table

- 2x or 4x temporal dithering

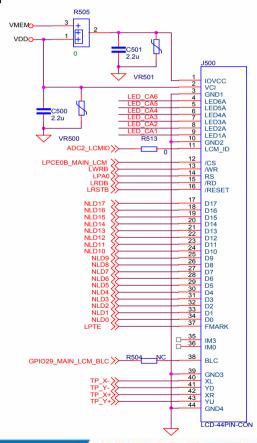

# LCM Design Note – CPU (Host) Interface

- LCM side must have FMARK(F\_Sync) frame update HW pin and need to connect to LPTE(W3) for tearing free Tier-1 performance

- LCM side IOVCC reserve VMEM(1.8V) & VDD(2.8V) option for 1.8V NAND application

- BB side power level

- VDD33\_NLD (pin AA9, AC9, W9) = LCM side IOVCC level

| MT6516 (Pin definition) |                                                                                                | LCM side       |

|-------------------------|------------------------------------------------------------------------------------------------|----------------|

| LPCE0B                  | W1                                                                                             | /CS            |

| LWRB                    | AA1                                                                                            | /WR            |

| LPA0                    | Y4                                                                                             | RS             |

| LRDB                    | Y2                                                                                             | /RD            |

| LRSTB                   | W7                                                                                             | /RESET         |

| NLD17~NLD0              | AA5, AF2, AP6, AE3, AB8, AD4,<br>AC7, AJ1, AH2, AL1, AG3, AF4,<br>AC5, AK2, AD6, AJ3, AD8, AN1 | D17~D0         |

| LPTE                    | W3                                                                                             | FMARK / F_Sync |

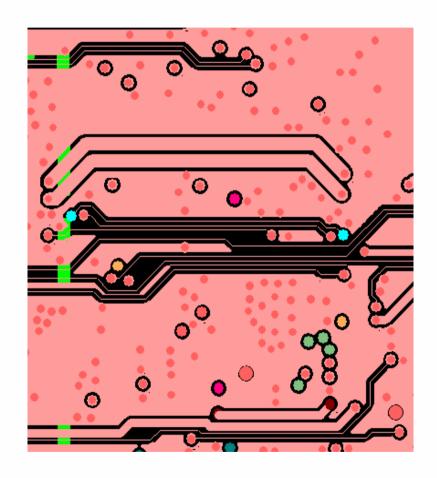

# LCM Design Note – RGB (DPI) Interface

- RGB (DPI) interface separated into two groups

- 3 wire (or 4 wire) SPI interface for LCM initial code setting

- Image databus (Dedicated pins and connect from BB to LCM directly)

- Layout notice

- DPICK, LSCK must well isolated by GND plane

- All Image signal length need to be equal as best.

- BB side power level

- VDD33 NLD (pin AA9, AC9, W9) = LCM side IOVCC(VDDI) level

| MT6           | 516 (Pin definition)    | LCM side |                                                                                                                                                                                                                                                                            | J4                                |             |

|---------------|-------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|

| LSCE0B        | V4                      | SPI_CS   | × 14.                                                                                                                                                                                                                                                                      | NC VDC                            | 4 OAVDD_LC  |

| LSDA          | U1                      | SPI_SDI  | LCM CS 10<br>LCM SPI SDA 11<br>LCM SPI SCK 13                                                                                                                                                                                                                              | SPI_CS<br>SPI_SDI VDD<br>SPI_CLKI | 3 OVDDIO_LC |

| LSCK          | U5                      | SPI_CLK  | LCM RST 15                                                                                                                                                                                                                                                                 | RST VSS                           | 5 12        |

| DPIVSYNC      | AA3                     | VSYNC    | DPIVSYNC   37   37   38   38   39   39   39   39   39   39                                                                                                                                                                                                                 | VSYNC VSS<br>HSYNC VSS<br>DENB    | 36          |

| DPIHSYNC      | W5                      | HSYNC    | NLD9 16<br>NLD9 17<br>NLD10 18                                                                                                                                                                                                                                             | DCK<br>B0<br>B1                   | $\Diamond$  |

| DPIDE         | AB2                     | DENB     | NLD11 19<br>NLD12 20<br>NLD13 21                                                                                                                                                                                                                                           | 82<br>83<br>84<br>85 YU           | 6 //yu      |

| DPICK         | AC1                     | DCK      | NLD14 22<br>NLD15 23<br>NLD16 24                                                                                                                                                                                                                                           | G0 YI<br>G1 XI<br>G2 XF           | 8 XYD       |

| NLD8 ~ NLD13  | AL1,AH2,AJ1,AC7,AD4,AB8 | B0 ~ B5  | NLD17 25<br>NLD18 26<br>NLD19 27                                                                                                                                                                                                                                           | G3<br>G4<br>G5                    |             |

| NLD14 ~ NLD19 | AE3,AB6,AF2,AA5,AG1,Y8  | G0 ~ G5  | DPIDE 39. DPIDE 35. NLD8 35. NLD8 16. NLD9 17. NLD10 18. NLD11 19. NLD12 20. NLD13 21. NLD14 22. NLD15 23. NLD16 24. NLD16 24. NLD17 25. NLD18 26. NLD19 27. NLD19 27. NLD20 28. NLD20 28. NLD21 29. NLD21 29. NLD22 30. NLD23 31. NLD23 31. NLD24 32. NLD24 32. NLD25 33. | R0<br>R1<br>R2                    |             |

| NLD20 ~ NLD25 | AC3,AA7,AD2,AE1,AB4,Y6  | R0 ~ R5  | NLD23 31<br>NLD24 32<br>NLD25 33                                                                                                                                                                                                                                           | R3<br>R4 LEDAN<br>R5 LEDCA        |             |

| LRSTB         | W7                      | RST      | N                                                                                                                                                                                                                                                                          | 1.1-11                            |             |

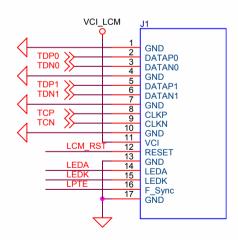

# LCM Design Note – MIPI (DSI) Interface

- All MIPI DSI pins are dedicated that connect from BB to LCM

- 1 CLK Lane + 2 Data Lanes

- F\_Sync for MIPI DSI command mode connect to dedicated pin LPTE

- BB side TVRT (pin G5) connect 1.8K 1% resistor to GND and close to BB

- Layout notice

- All signal pairs need to 50ohm impedance matching for single end and 100ohm for differential

- All signal length need be equal and well shielded by GND plane

- BB side power level

- VDD33 NLD (pin AA9, AC9, W9) = LCM side IOVCC(VDDI) level

- DVDD12\_MIPI (J7, K8) connect to VCORE(1.2V)

- DVDD28\_MIPITX (H8, J9), DVDD28\_MIPIRX(J5), AVDD28\_MIPITX (G7), and VDD33\_MIPI (L11) connect to VDD (2.8V)

| MT6516 (Pin definition) |    | LCM side    |

|-------------------------|----|-------------|

| PAD_TDP0                | C1 | TDP0        |

| PAD_TDN0                | D2 | TDN0        |

| PAD_TDP1                | A3 | TDP1        |

| PAD_TDN1                | B4 | TDN1        |

| PAD_TCP                 | B2 | TCP         |

| PAD_TCN                 | C3 | TCN         |

| LRSTB                   | W7 | RESET       |

| LPTE                    | W3 | F_Sync / TE |

# MEDIATEK

# High Speed Memory Layout Rule Mobile DDR SDRAM

Copyright © MediaTek Inc. All rights reserved.

### **Outline**

- Overview

- High speed memory layout considerations

- Placement

- Suggested routing order

- Ground/Power plane

- Signal layout

- Other general layout considerations

- Check list

### Overview

### **DDR SDRAM signals**

- We can categorize DDR SDRAM interfaces into 4 groups as follows.

- Signal quality could be degraded by any PCB layout issue.

- We must take care of different groups of DDR SDRAM.

| Group   | Signal Name                            | Description                                                                               |  |

|---------|----------------------------------------|-------------------------------------------------------------------------------------------|--|

| Data    | DQ[0:15]<br>DQS[0:1]<br>DM[0:1]        | Data Bus<br>Data Strobe<br>Data Mask                                                      |  |

| Clock   | CLK<br>CLK#                            | Memory Differential Clock<br>Memory Inverted Differential Clock                           |  |

| Command | A[0:15]<br>BA[0:1]<br>RAS<br>CAS<br>WE | Address Bus<br>Bank Select<br>Row Address Select<br>Column Address Select<br>Write Enable |  |

| Control | CKE<br>CS                              | Clock Enable<br>Chip Select                                                               |  |

- It is recommended that the PCB layout of memory interface is the first priority for your design.

- We can check memory PCB layout characteristics in the following order:

- 1. Placement

- 2. Suggested routing order

- 3. Ground/Power plane

- 4. Signal layout

- 5. Other general layout considerations

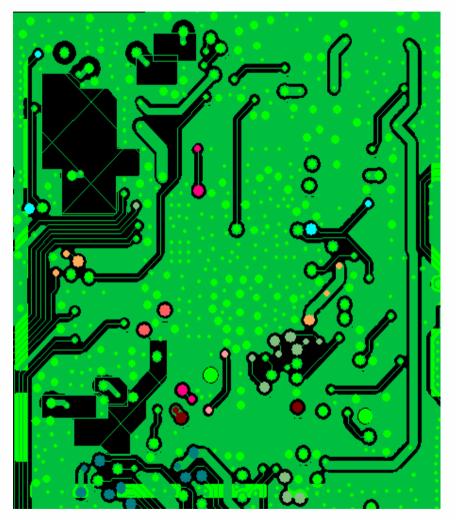

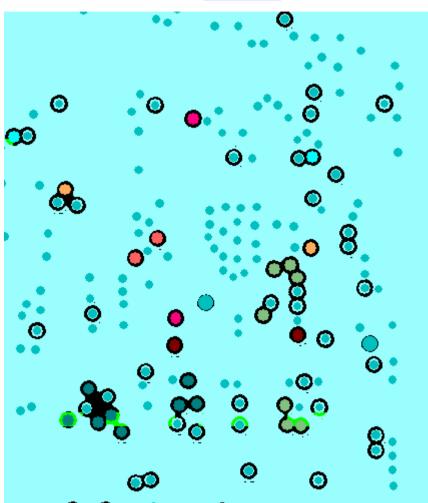

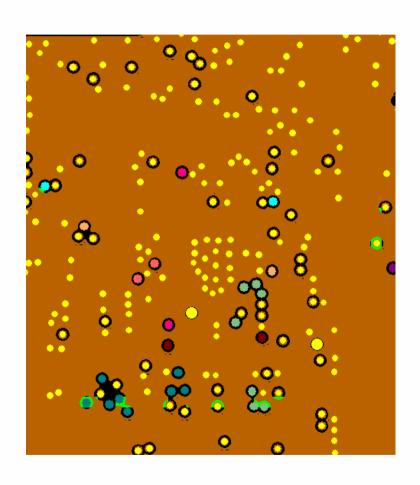

#### Placement

- Memory device must place as close to BB Chip as possible

- Avoiding extra long trace (Max trace1500mil)

- Avoiding other high frequency devices place close to Memory

- Route these traces smoothly, reduce the via counts and avoiding traces interlace if possible

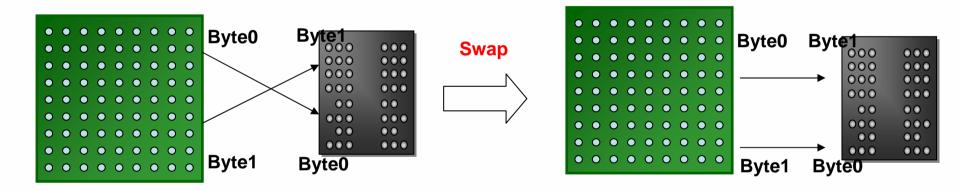

- You can swap byte in order to reduce traces interlace if there has restriction in placement (only for SD/DDR RAM)

- "Swap byte" means to connect DQS0 from BB chip to memory DQS1 in order to reduce the interlacing of data traces, e.g. D[0:7] from BB chip to memory D[8:15].

- Note: Swap the corresponding DQS ,DQM and DQx at the same time.

### Layout routing

- Please route traces by the following order:

- 1. Power/GND plane

- 2. Data group

- 3. Clock group

- 4. Command/Address/control groups

- Because high frequency signal integrity is highly related to solid ground and power plane, data groups are operating at twice the clock frequency.

- It is recommended that the designer takes care of the layout routing in the very beginning of the design.

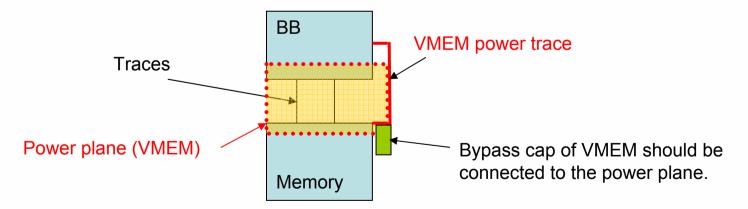

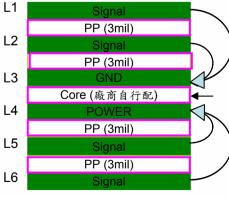

### Ground/Power plane

- A solid power/ground plane must be provided near all traces routing layers.

- It will minimize the ground return current to get better performance.

- There are 2 methods for reference:

- 1. It is recommended all traces are routed above a solid GND plane, and there is a power plane (memory power domain) under the GND plane if possible.

- e.g. 1st layer : Traces

2<sup>nd</sup>/3<sup>rd</sup> layer: Trace (strongly recommended - the same group of traces routed on the same layer)

4rd layer: GND

5th layer: Power plane (VMEM) if possible, which is under the traces of memory interface.

2. All traces are routed above a solid GND plane, and under a DC power plane (VBAT domain) to provide good shield (the traces of memory interface protected by VBAT and GND)

e.g. 1st layer: VBAT

2nd layer: Trace (strongly recommended - the same group

of traces routed on the same layer)

3rd layer: Trace

4th layer: GND

Note: All power trace bypass capacitors must be placed as close to the devices' power pins as possible, and all capacitor's GND should have the shortest and widest trace to the GND plane.

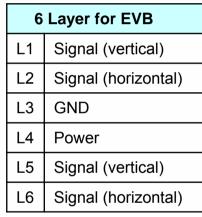

# **Suggested Layer Definition**

- Layer definition

- 相鄰層避免走平行線

Stack-up

PP厚度較薄,L1及L2的Signal有最短的 return path

建議CORE的厚度最厚,以保持其它層的PP厚度較薄

PP厚度較薄,L5及L6的Signal有最短的 return path

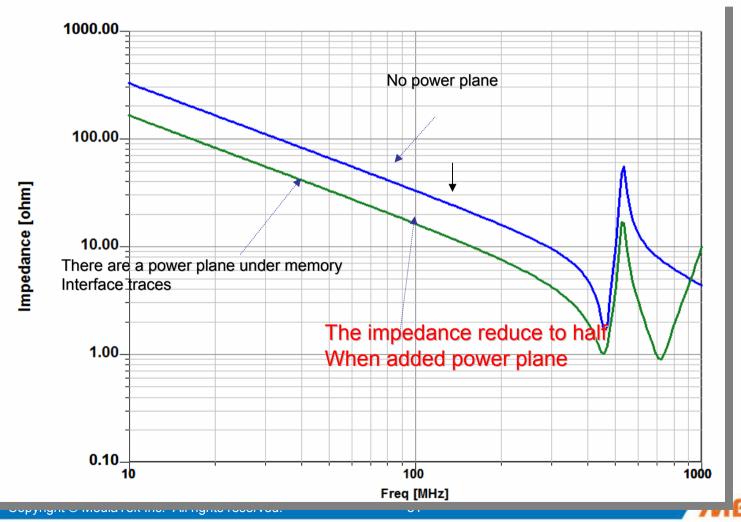

If we take a good power plane under traces, we can get good power trace impedance performance.

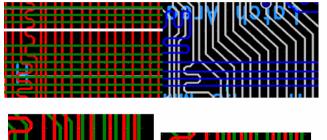

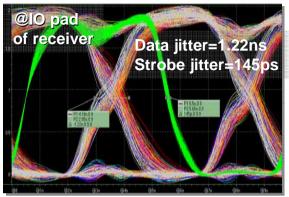

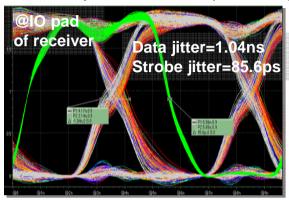

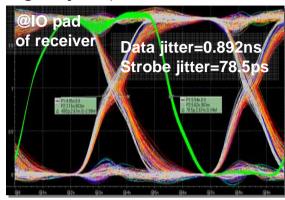

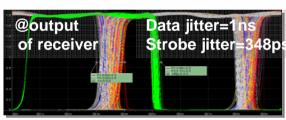

## High Speed Memory Layout Considerations Confidential B

Add a power plane on PCB to enhance performance (reducing signal jitter)

Only power trace **Not good**

Added a small power plane under BB chip Better

Added power plane under BB chip and DRAM Best

Copyright ©

rved.

### Signal layout

- We categorized all signals into 4 groups, prioritized as follows:

- 1st priority: Data group

- 2nd priority: Clock group

- 3rd priority: Control/Command groups

- If possible, control trace impedance between BB chip and DRAM, trace impedance is related to PCB dielectric constant, trace width, trace thickness, and routing method (using microstrip or stripline).

- The performance will get better if signal trace impedance is under control.

| Group             | Signal Name                            | Description                                                                               |  |

|-------------------|----------------------------------------|-------------------------------------------------------------------------------------------|--|

| Data              | DQ[0:15]<br>DQS[0:1]<br>DM[0:1]        | Data Bus<br>Data Strobe<br>Data Mask                                                      |  |

| Clock             | CLK#                                   | Memory Differential Clock<br>Memory-inverted Differential Clock                           |  |

| Command           | A[0:15]<br>BA[0:1]<br>RAS<br>CAS<br>WE | Address Bus<br>Bank select<br>Row Address Select<br>Column Address Select<br>Write Enable |  |

| Control CKE<br>CS |                                        | Clock Enable<br>Chip Select                                                               |  |

### 1. Data group (1/2)

DQx and DQS must be routed in a group and routed in the same layer and reduce via counts if possible.

e.g.

D[0:7] is aligned to DQS[0];

D[8:15] is aligned to DQS[1].

So, D[0:7] must be routed in a group with DQS[0], and D[8:15] must be routed in a group with DQS[1].

| Group | Signal Name                     | Description                          |

|-------|---------------------------------|--------------------------------------|

| Data  | DQ[0:15]<br>DQS[0:1]<br>DM[0:1] | Data Bus<br>Data Strobe<br>Data Mask |

- 1. Data group (2/2) (Remind : power/GND plane is the most important)

- Within the same data group: (Max. trace length 500 mil )< Trace length < (Max. trace length)</li>

- Between different data group: (Max. trace length 500 mil )< Trace length < (Max. trace length)</li>

- | DQS Clock trace length | < 300 mil

- If possible, control data trace impedance to ensure it meets the requirement (please check input impedance of memory).

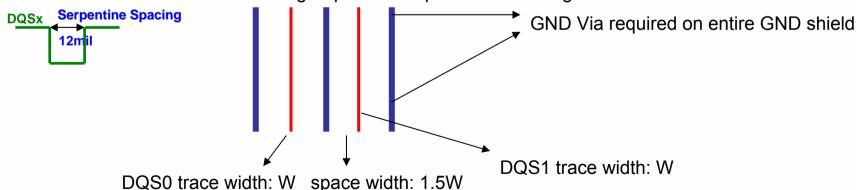

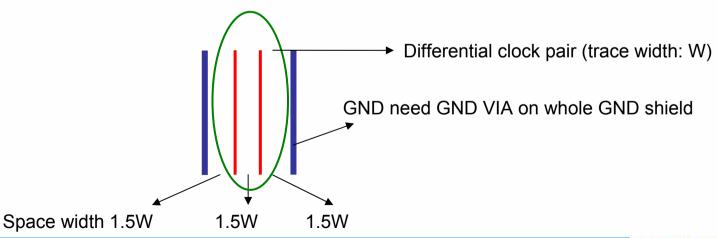

- Within the same group if DQx trace width is W, the space between DQx is 1.5 W.

- To reduce the crosstalk on DQSx , GND shielding is required.

- If the trace width is W, the trace space between DQSx and GND is at least 1.5W, and the width between DQS0 and DQS1 is at least 3W.

- Do not route data group traces in parallel for a long distance.

#### 2. Clock group (1/2)

- There are a differential pair of high speed clocks in the DDR SDRAM memory device, so we need to take care of these traces to ensure the clock integrity.

- Route these 2 clock traces in parallel and keep equal trace length.

- Control clock trace impedance (please check memory device). If clock trace is W the space between clk and /clk is at least 1.5W and there need GND shield wrap around the clock differential pair. The space GND and Clock trace at least 1.5W, and the GND shield need enough GND via if we can not give enough GND via, we would rather take GND shield off, and the space to adjacent signals is at least 2W.

### 2. Clock group (2/2)

- Away from other high frequency traces

- Each clock trace must have solid power and ground plane near the entire route.

- Each clock trace is recommended to route on the same layer to reduce Via number, and to keep the same trace characteristics.

### 3. Control/Command groups

- Every trace must have solid power and ground plane near the entire route.

- Every trace is recommended to route on same layer to reduce Via number, and to keep the same trace characteristics.

- Route address traces from priority A0 (most toggled) to A15 (less toggled), and A0 should be close to ground if possible. |Trace length - Clock trace length| < 500 mil</li>

```

Within CMD/ADR group:

|Max. (CMD/ADR trace length) – Min. (CMD/ADR trace length)|

<250 mil

```

- Remind : power ground is the most important , you just need to meet the traces match criterion as possible

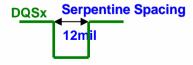

- If serpentine is needed, the spacing is at least 12mil

### **Check List**

- Placement

- Memory device must placed as close to the BB chip as possible.

- Avoid extra long trace (Max. trace: 1500 mil) and other high frequency devices placed close to memory

- Route these traces smoothly, reduce the Via counts and avoiding traces interlacing if possible

- Considerations on ground/power plane (power/GND plane is the most important )

- It is recommended all traces to be routed above a solid GND plane, and there is a power plane (memory power domain) under GND plane if possible.

```

e.g. 1st layer: Traces

2nd layer: Trace (strongly recommended — the same group of traces routed on the same layer)

3rd layer: GND

4th layer: Power plane (VMEM) if possible, the plane is under the traces of memory interface.

```

Or all traces are routed above a solid GND plane, and under a DC power plane (VBAT domain) to provide a good shield (the traces of memory interface protected by VBAT and GND).

```

e.g. 1st layer: VBAT

2nd layer: Trace (strongly recommended — the same group of traces routed on the same layer)

3rd layer: Trace

4th layer: GND

```

- Trace length is as match as possible, All traces refer to clock, within 500mil length difference is acceptable (DDR, DQS and DQ is a group, and DDR clock,/clock are within 100mil)

- If serpentine is needed, the spacing is at least 12mil

Confidential B

# MEDIATEK

# MT6516 USB Design Notes

**Schematics and Cable Design**

Copyright © MediaTek Inc. All rights reserved.

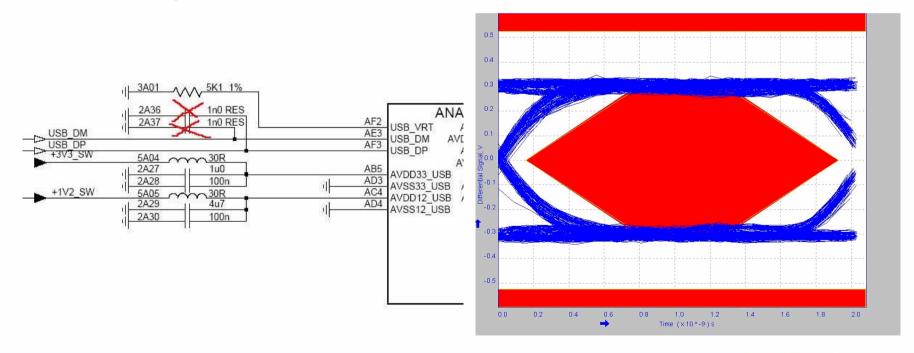

### MTK USB2.0 Solution Introduction

- This document introduces MTK USB2.0 design and some points for attention.

- MTK USB2.0/ OTG device can operate at USB2.0 High-Speed (HS) mode (480Mb/s) and Full-Speed (FS) mode (12Mb/s).

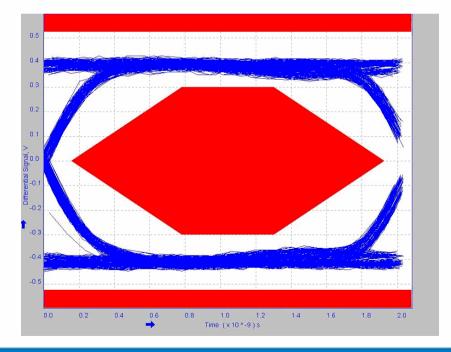

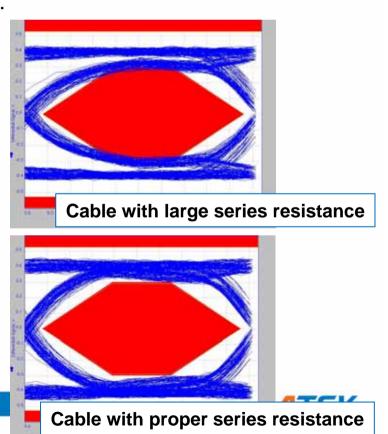

General HS eye diagram is shown as below. The output swing is differential 0.4V. Bad eye diagram will lead to certification fail or signal

integrity problem.

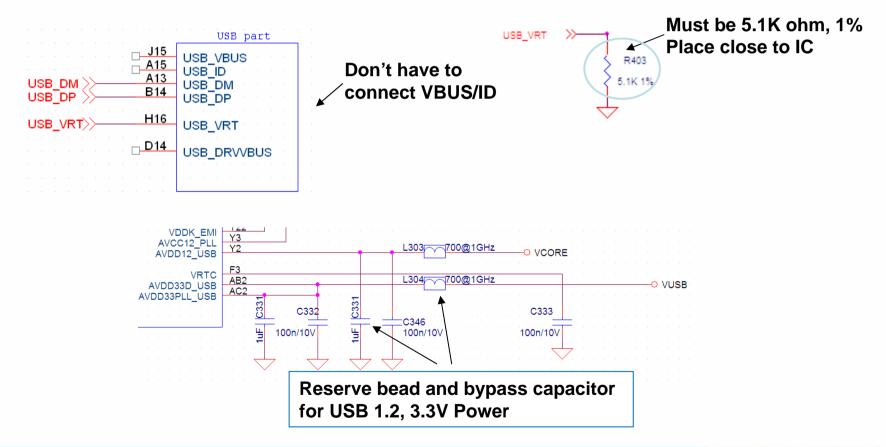

### **USB Pin Definition**

- USB2.0 pin out description.

- General pins

| Pin | Symbol       | Type | Description                                              |

|-----|--------------|------|----------------------------------------------------------|

| 1   | PAD_USB_VBUS | Ю    | * Comparator used for detecting changes of VBUS voltage. |

| 2   | PAD_USB_DM   | Ю    | USB serial differential bus (minus)                      |

| 3   | PAD_USB_DP   | Ю    | USB serial differential bus (positive)                   |

| 4   | AVDD3_USB    | VDD  | Analog 3.3V supply                                       |

| 5   | AVSS33_USB   | GND  | Analog 3.3V ground                                       |

| 6   | PAD_USB_VRT  | Ю    | Analog 5.1K reference resistor                           |

| 7   | AVDD12_USB   | VDD  | Analog 1.2V supply.                                      |

| 8   | AVSS12_USB   | GND  | Analog 1.2V ground                                       |

### Optional pins for supporting OTG

| Pin | Symbol     | Туре | Description                                                       |

|-----|------------|------|-------------------------------------------------------------------|

| 9   | PAD_USB_ID | Ю    | Optional function for USB OTG ID pin for detecting slave plug in. |

### Schematics Design for USB2.0 Device (2/2)

MT6516 (Device Only)

### **Schematics Design for USB2.0 High Speed**

- Beware of USB\_VRT pin should keep away from noise source and high speed clock data like camera databus.

- Reserve 0402 cap (NC) on DP/DM for ESD protection and rise time/fall time tuning for USB-IF compliance test.

- If want to get USB-IF OTG logo, should use micro-AB connector.

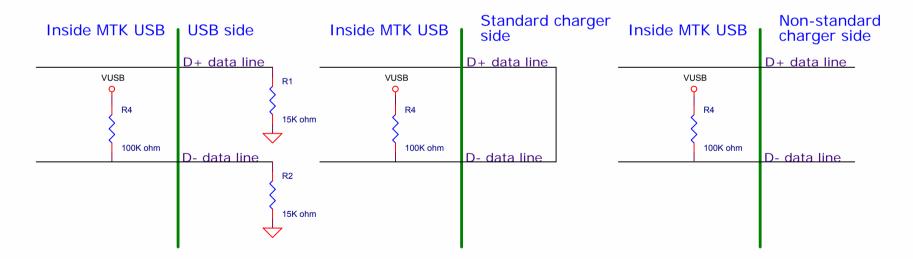

### **USB/ Charger Detection**

- Used for MT6516 and later on MTK ICs (MT6268/MT6516/MT6253)

- When charger interrupt happens, turn on D- pull high 100K ohm resistor and check the polarity of D-

- If the D- is LOW, it is USB charger, otherwise it is a standard or a nonstandard charger

### **USB/ Charger Detection (Cont.)**

- Then check whether it is standard or non-standard charger. Turn

on D+/D- internally 15K ohm pull low resistor and D+ 1.5K ohm

pull high resistor at the same time.

- Check D- polarity. If the D- is HIGH, it is standard charger, otherwise it is a non-standard charger.

### High Speed USB Layout Checklist (1/2)

- General design and layout rules

- With minimum trace lengths, route clock source and HS USB differential pairs first. Keep maximum possible distance between clocks/periodic signals to USB differential pairs to minimize crosstalk.

- Route HS USB signal pairs together with equal length by using a minimum vias and corners. This reduces signal reflections and impedance changes.

- Maintain parallelism between USB differential signals with the trace spacing needed to achieve 90 ohms differential impedance.

- When it becomes necessary to turn 90 °, use two 45 ° turns or an arc instead of making a single 90 ° turn. This reduces reflections on the signal by minimizing impedance discontinuities.

- Do not route USB traces under crystals, oscillators, clock synthesizers, magnetic devices or ICs that use and/or duplicate clocks.

### High Speed USB Layout Checklist (2/2)

- General design and layout rules (Conti.)

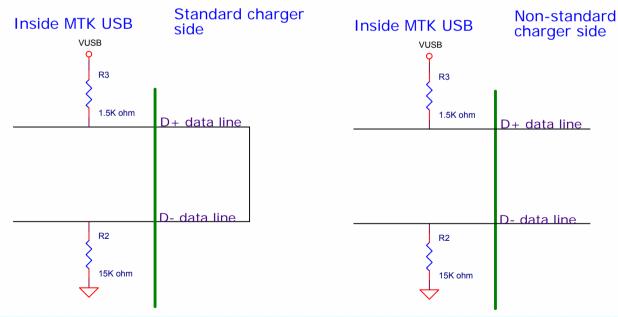

- Stubs on HS USB signals should be avoided, as stubs will cause signal reflections and affect signal quality.

- Avoid crossing over anti-etch if possible. Crossing over anti-etch (plane splits) increases inductance and radiation levels by forcing a greater loop area. Likewise, avoid changing layers with high-speed traces as much as practical.

- Keep HS USB signals away from high current area. The current transient during state transitions could induce noise to USB.

### **Stubs**

Avoid creating unnecessary stubs on data lines, if a stub is unavoidable (for example: ESD issue), please keep the stub as short as possible.

### **Poor Routing Techniques**

- Cross a plane split.

- Creating a stub with a test point.

- Failure to maintain parallelism. Failure to maintain parallelism of USB2.0 data lines Proper routing technique maintains spacing guidelines **Ground or** Power plane Don't cross **Avoid creating stubs** plane splits 100 Copyright © MediaTek Inc. All rights reserved.

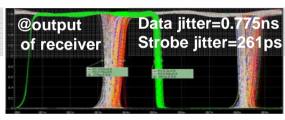

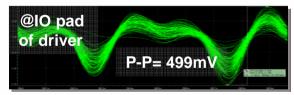

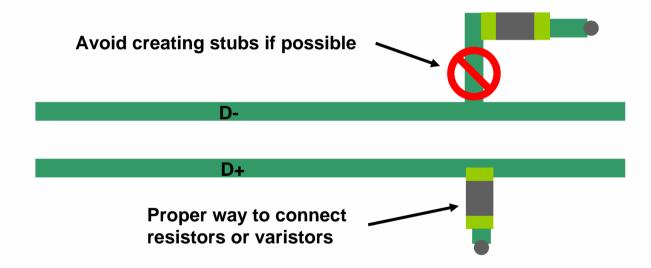

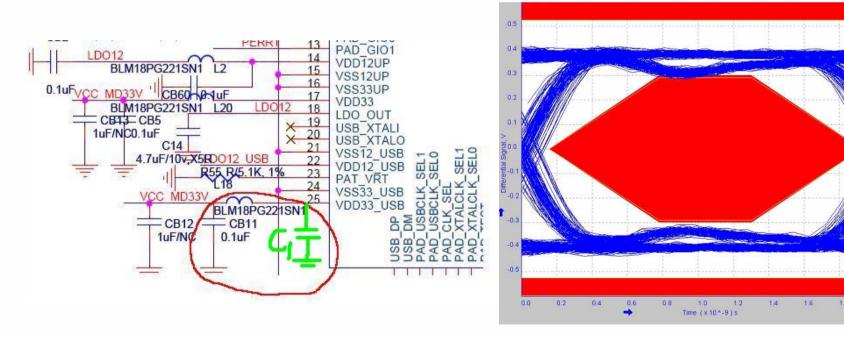

## Case Study (1/5)

- Case 1:

- 2A36/2A37 should be removed. Large cap at USB\_DP/USB\_DM will lead to bad jitter performance.

- Measured eye at board is shown below. It will occur turn-around error at system application.

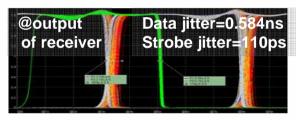

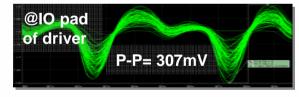

### Case Study (2/5)

- Case 2:

- After bead, at least 0.1uF capacitor between VDD33\_USB, VDD12\_USB and ground must be added as follows.

- Measured eye diagram has bad jitter performance.

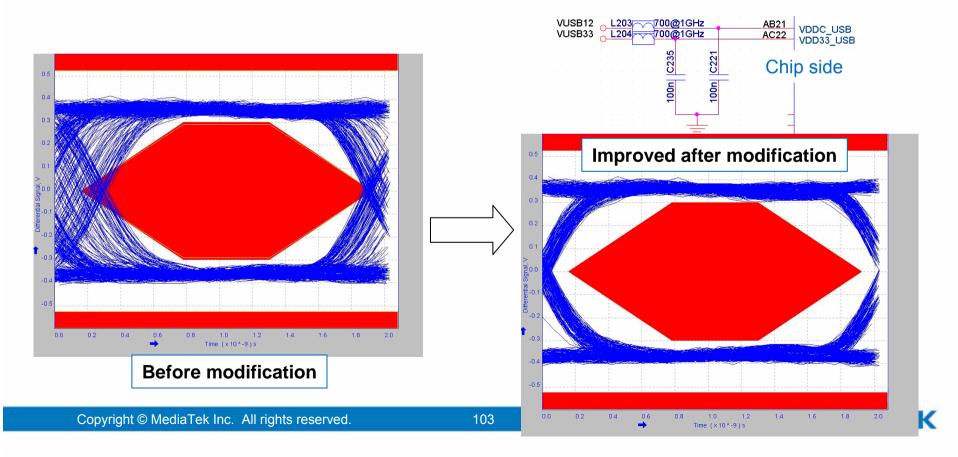

### Case Study (3/5)

- Case 3:

- Some time we got worse jitter due to poor layout, then VUSB33 and VUSB12 are coupled by noise.

- It is improved by increasing bypass capacitor C221 and C235.

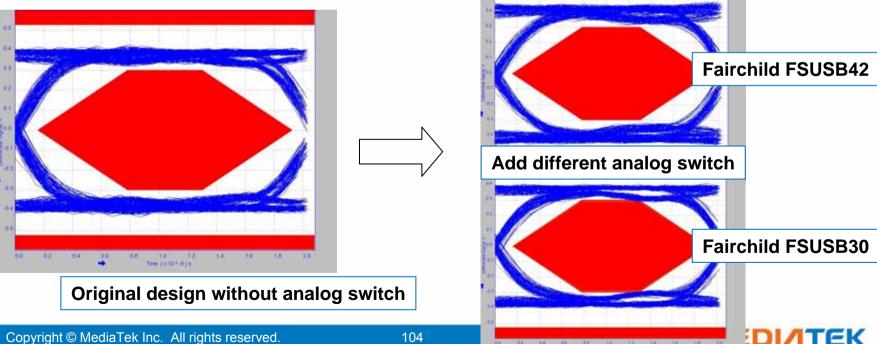

## Case Study (4/5)

#### Case 4:

- Customer wants to share USB data pins with audio/UART pins through the same 5-wire USB connector by using analog switch.

- Different analog switches cause different attenuation of signals; please make sure component and layout will get proper eye diagram.

No suggestion on using analog switch, 11-pin USB connector could be used

instead.

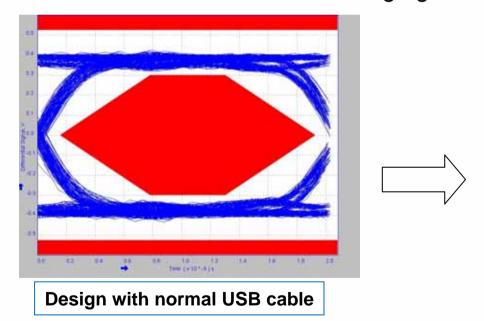

### Case Study (5/5)

- Case 5:

- Sometimes customer may design a special connector for USB, such as 18-pin I/O.

- Poor cable will cause poor performance.

- Please follow USB cable design guide.

### **Conclusions**

- Layout and component selection are critical for USB2.0 high speed performance

- Need to follow the design rule or there might be compatibility issue happens

- Grounding and shielding are both critical when design USB2.0 high speed capable cables

- It can maintain USB signal quality with little jitter/ signal distortion caused by cable design

- Please refer to "MTK USB2.0/ OTG Design Guide " for more detail.

Confidential B

# MEDIATEK

# MT6516 Factory Mode & Engineer Mode Notice

Copyright © MediaTek Inc. All rights reserved.

# **Engineer Mode and Factory mode**

- Factory mode

- Enter phone menu

- Enter "\*#66\*#", then dial

- Engineer mode

- Enter phone menu

- Enter "\*#3646633#", then dial

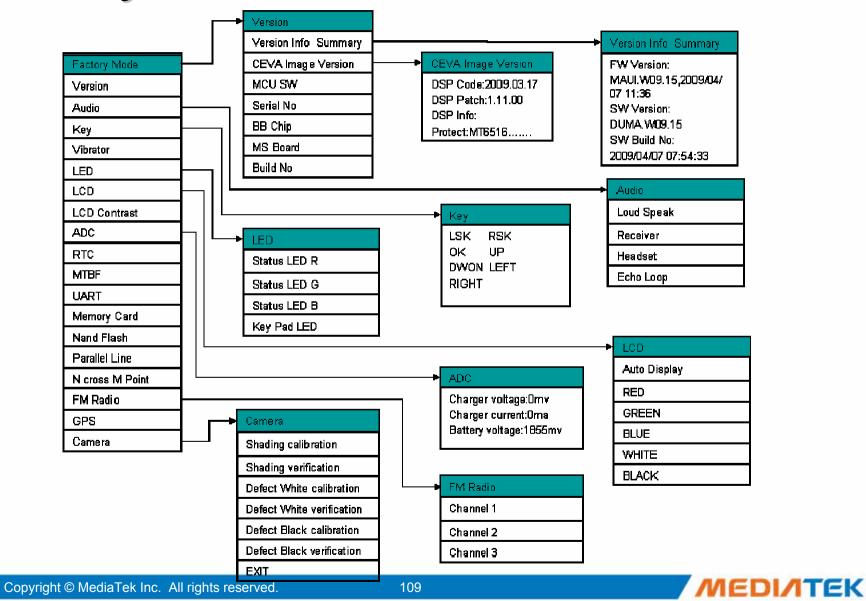

## **Factory Mode Menu Tree**

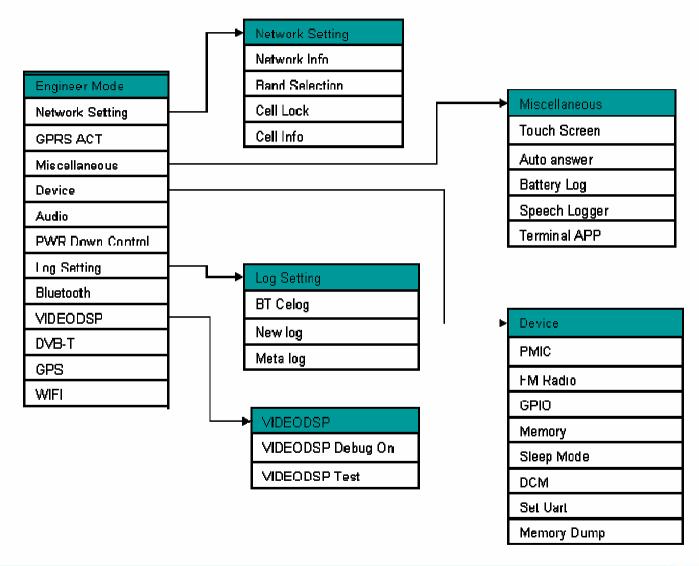

# **Engineer Mode Menu Tree**

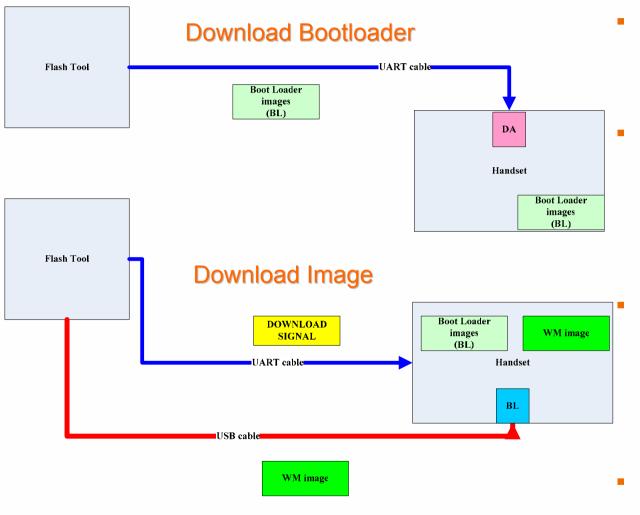

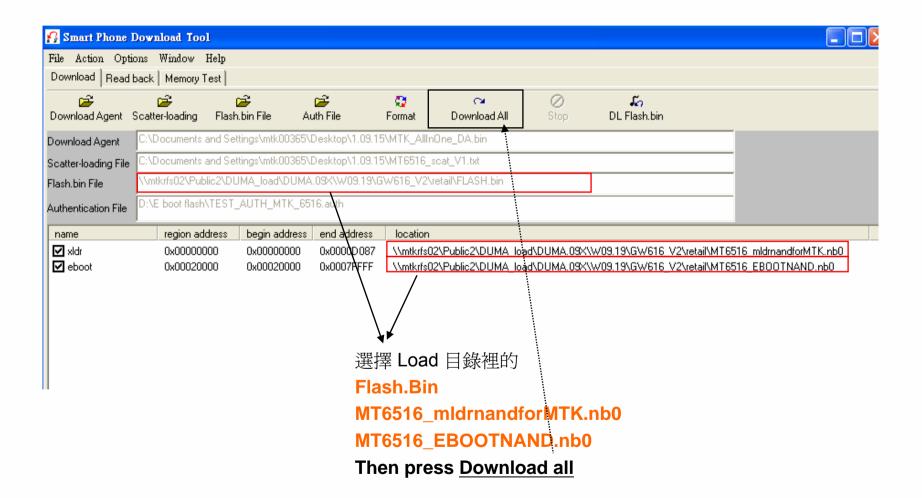

#### Flash Tool Download Flow

- Bootloader Download

- Use UART1 to download bootloader

- Windows Mobile image download

- Connect both UART1 and USB to download full WinMo image

- Flash tool can combine the two steps above.

(Must connect both UART1 and USB to PC first!)

Please refer to flash tool document in detail.

#### **Download tool**

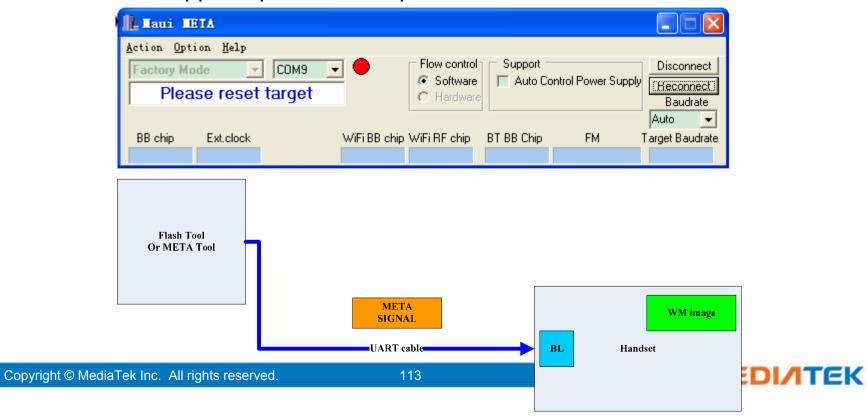

# **META Link (AP Side)**

- Install Smartphone META tool.

- How to enter META mode (UART1)

- If target have not been in META mode, click "Reconnect" button, then connect phone;

- Phone will power on and enter into META mode automatically

- UART can support up to 115200bps baud rate

# **META Link (Modem Side)**

- Install smartphone META tool (for first time)

- Link UART4 on handset to PC

- Open hyper terminal on PC and set correct COM port and parameters.

- Press "send key" and "end key" to power on.

- Set boot to META mode: Enter 9->3->1

- Enter 0->0, continue to boot to META mode

- Close hyper terminal, switch UART4 to UART1. (UART1 link to PC)

- Wait about 12 seconds.

- Execute META tool

- Choose UART and enable "connect target already in META mode" in option menu.

- Can backup/restore calibration data in "update parameter" as feature phone.

Confidential B

# MEDIATEK

# MT6516 Memory Support Plan

MTK MVG (Memory Verification Group)

#### **EDGE Smart Phone**

| Segment          | EDGE Smart Phone                                        |

|------------------|---------------------------------------------------------|

| Platform         | MT6516                                                  |

| MCP              | (2G/1G) +1G (x32)                                       |

| IVICP            | NAND + MobileDDR MCP                                    |

| MCP Type         | NAND(SLC, 2K page) + 133/166MHz MobileDDR               |

|                  | Samsung K522F1GACM-A060 (2G+1G, 1.8V*, BGA137) → W0919  |

|                  | Elpida EHD013011MA-60 (2G+1G, 1.8V, BGA137) → W0921     |

|                  | Toshiba TYA000B801CFLP40 (2G+1G, 1.8V, BGA137) → W0922  |

|                  | Numonyx NANDBAR4N5BZBC5E (2G+1G, 1.8V, BGA137) → W0923  |

|                  | Micron MT29C2G24MAKLAJA-6 (2G+1G, 1.8V, BGA137) → W0924 |

| Memory P/N       | Hynix H8BCS0PJ0MCP-56M (1G+1G, 1.8V, BGA137) → W0925    |

| (Week available) | Samsung K522H1GACD-A060 (2G+1G, 1.8V, BGA137) → W0926   |

| , , , , , ,      | Micron MT29C1G24MAVLAJA-6 (1G+1G, 1.8V, BGA137) → W0927 |

|                  | Micron MT29C1G24MACLAJA-6 (2G+1G, 1.8V, BGA137) → W0928 |

|                  |                                                         |

|                  |                                                         |

|                  |                                                         |

|                  |                                                         |

<sup>\*</sup> Voltage supply of NAND flash.

\*\* For devices not included in the weeks available, please contact with MTK PM for status update.

Confidential B

# MEDIATEK

# **Appendix**

Peripherals Design Notice (GPS/DTV)

Copyright © MediaTek Inc. All rights reserved.

Confidential B

# MEDIATEK

# MT6516 WIFI/BT Co-module Application Note

2009/4 WCP/RP1/W.Wei

#### **Outline**

- Module function block and reference design

- Module function block

- Module reference design

- > Reference interface assignment

- > Key component list

- Schematic and layout design guide

- Schematic design guide

- Layout design guide

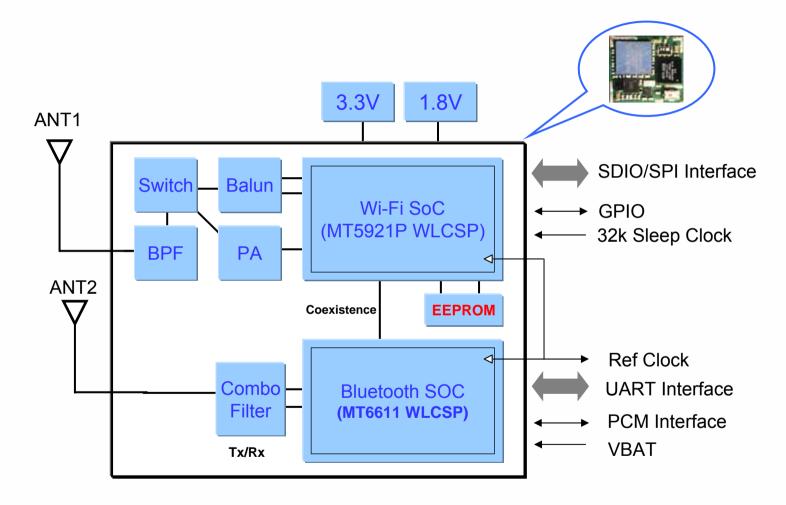

#### Wi-Fi/BT Combo Module Product Definition

- Full-featured Wi-Fi 802.11b/g and BT 2.1 + EDR combo module

- Small-size package: 9.5×10.5×1.4 mm LGA (< 10×10 mm)</li>

- MTK's proprietary superior Wi-Fi/BT co-existence performance

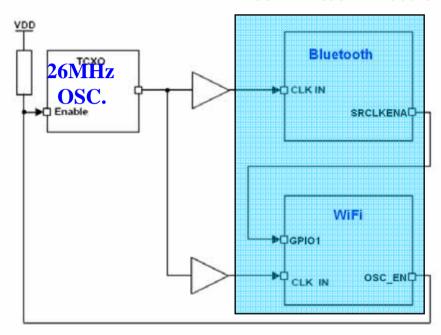

- Wi-Fi and BT co-existence shares the 26 MHz clock frequency.

- Metal EM interference shielding

- Antenna: Dual antenna (mandatory)/Single antenna (optional)

- RoHS complaint

Sample: Sep. 2008

MP: 2009/02

#### **MTK Combo Module Block Diagram**

#### Wi-Fi Features

- Advanced Wi-Fi features

- 802.11b/g/e/i/h/k/w compatible

- IEEE 802.11e QoS (WMM/WMM-PS)

- Background scan for specific SSID networks

- IEEE 802.11i advanced security (WEP/TKIP/AES/WPA/WPA2)

- 802.11e optional U-APSD, DLS

- 802.11 power saving mode

- Wakeup by specific packet (pattern search)

- Thermo-sensor to resist temperature change

- Voice over WLAN (VoWLAN)

- UMA (Unlicensed Mobile Access) technology

- VoIP over WLAN

- Software support

- Win CF 5.0

- Win Mobile v5.0/6.1

- Win Mobile v7.0 (planning)

- Linux v2.6 (planning)

- Wi-Fi certified

#### **Bluetooth Features**

#### Radio features

- Fully compliant with Bluetooth 2.1+EDR

- Low-IF Architecture with high performance linearity

- Supports Bluetooth class 2 and 3

- Tx transmit power: 4 dBm

- 90 dBm sensitivity with excellent interference rejection performance

- 3.5 x 3.5 x 0.6 mm (max.), 0.5 mm pitch WLCSP

#### Baseband features

- Up to 7 simultaneous active ACL links

- Supports 3 simultaneous SCO and eSCO links SCO and scatternet

- Supports lower power mode (Sniff, Hold and Park mode)

- Ultra low power consumption in sleep mode

- Supports AFH and PTA for WLAN/BT coexistence

#### Software features

- Supports standard HCI interface

- Supports more than 15 profiles in MediaTek platform

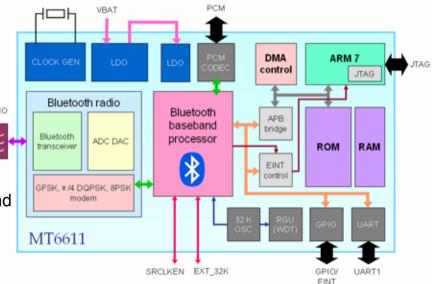

#### **MT6611 Function Block**

#### **Module Share Clock with Daisy chain**

- WiFi power need to power on to keep daisy chain working normally.

- WiFi can be shut down only as BT power off.

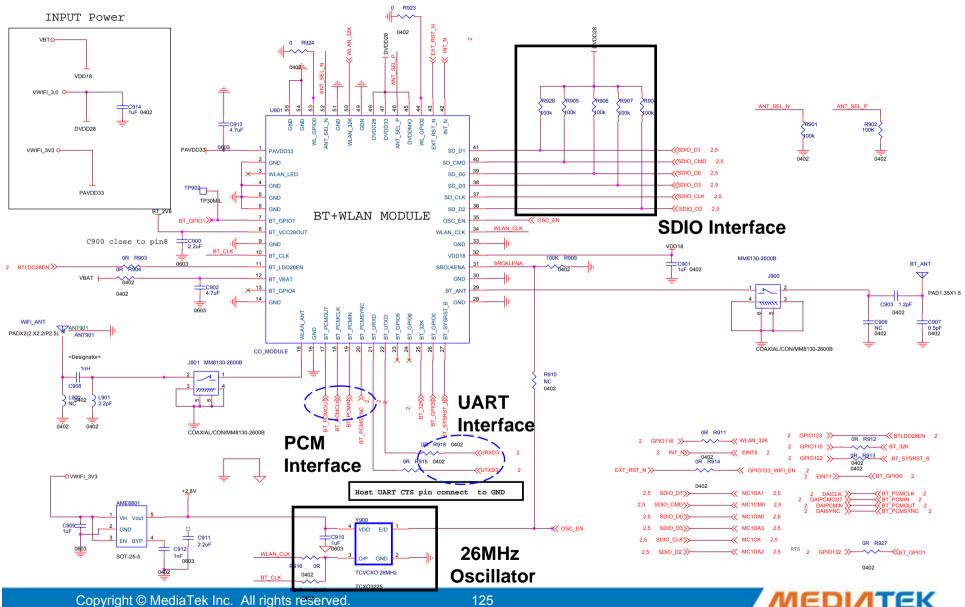

#### **Co-module Reference Design**

#### Confidential B

#### **Interface Assignment**

| Type    | Pin     | Function       |  |

|---------|---------|----------------|--|

| I/O     | GPIO133 | WIFI_RSTB      |  |

| 1/0     | GPIO116 | WLAN_32K       |  |

|         | MC1CM0  |                |  |

|         | MC1DA0  |                |  |

| T. (T.) | MC1DA1  | SDIO           |  |

| I/F     | MC1DA2  | 3010           |  |

|         | MC1DA3  |                |  |

|         | MC1CK   |                |  |

| I/O     | INT5    | WiFi_interrupt |  |

| Type | Pin       | Function     |

|------|-----------|--------------|

| I/O  | GPIO122   | BT_RSTB      |

| 1/0  | GPIO115   | BT_32K       |

|      | UTXD3     | HADT         |

|      | URXD3     | UART         |

| T /T | DAICLK    | РСМ          |

| I/F  | DAIPCMOUT | . PGIVI      |

|      | DAIPCMIN  |              |

|      | DAISYNC   |              |

| I/O  | INT1      | BT_interrupt |

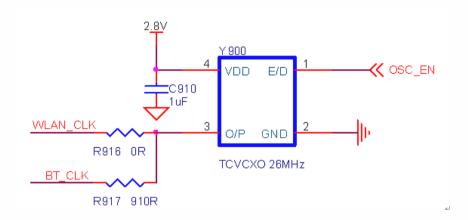

#### **26MHz Oscillator List**

•MT6611 PCM/UART power domain support 2.8~3.3v, not support 1.8V

| Item       | Part number                                | Vendor | Designator |

|------------|--------------------------------------------|--------|------------|

|            | SMA026000-3DR3T0<br>(Load 15pF, 2.8V~3.3V) | Aker   | Y900       |

| 26MHz      | 8W26000011<br>(Load 15pF, 2.8V~3.3V)       | TXC    | Y900       |

| Oscillator | SG-310SCN.<br>(Load 15pF, 2.8V~3.3V)       | EPSON  | Y900       |

|            | FK2600008<br>(Load 15pF, 2.8V~3.3V)        | 亞陶     | Y900       |

#### WiFi interface Selection

|      | TRSW_N | TRSW_N | ANT_SEL_P |  |

|------|--------|--------|-----------|--|

| SDIO | 0      | 0      | 0         |  |

| SPI  | 0      | 0      | 1         |  |

#### **Main Clock Frequency Selection**

|   |       | WLAN_ACT | ANT_SEL_P | OSC_FREQ0 |                         |

|---|-------|----------|-----------|-----------|-------------------------|

| _ | 20MHz | 0        | 0         | 0         |                         |

| ı | 26MHz | 0        | 0         | 1         | <ul><li>Fixed</li></ul> |

|   | 40MHz | 0        | 1         | 0         | <b></b>                 |

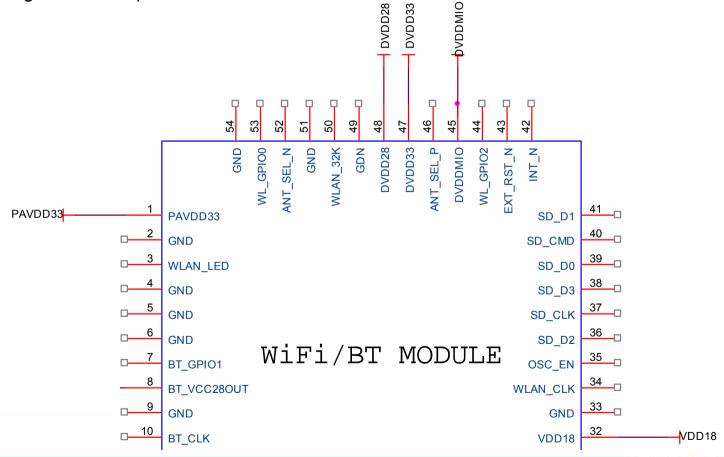

#### Schematic Design Guide(1)\_Power Supply

- •PAVDD33 is a dedicated input pin for module internal PA power supply and please connect it to 3.3V.

- ●DVDD28, DVDD33 and DVDDMIO are the WiFi portion digital IO power source, please connected to 3.0V for optimum Tx performance.

●VDD18 is the WiFi RF/analog/digital LDO input pin and can be connected to DC/DC 1.8V power source without degrading the module performance.

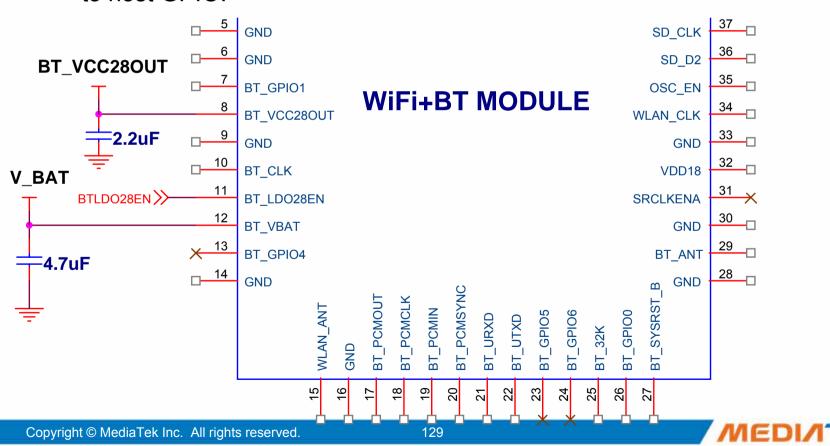

# **BT Power Domain (2)**

- Distributed into two domains: V\_BAT and 2.8V

- V\_BAT power source could come from phone battery and BT\_VCC28 is the internal LDO output pin.

- The BT 2.8V internal LDO was controlled by BTLDO28EN pin connected to host GPIO.

#### Schematic Design Guide(3)\_Clock Source

- ●The WiFi/BT device can share a same clock with a daisy chain function .This mechanism allows Bluetooth can work normally without extra power consumption even WiFi operating in the sleep mode.

- ●The oscillator with 2.8~3.3V operated voltage, 20ppm tolerance and 15pF load capacitance is recommended

- •32KHz clock for device sleep mode

- The 32KHz source come from BB GPIO output...

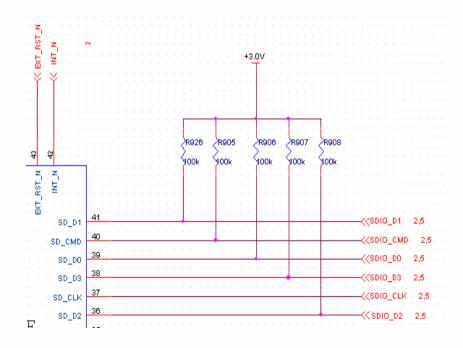

#### Schematic Design Guide(4)\_Interface

- •Please add 100K pull resistors for the SDIO data pin except SD\_CLK pin.

- •For BT UART interface, please note to connect the MT6516 host UART CTS pin to GND.

#### **BT UART Interface**

#

#### WiFi SDIO Interface

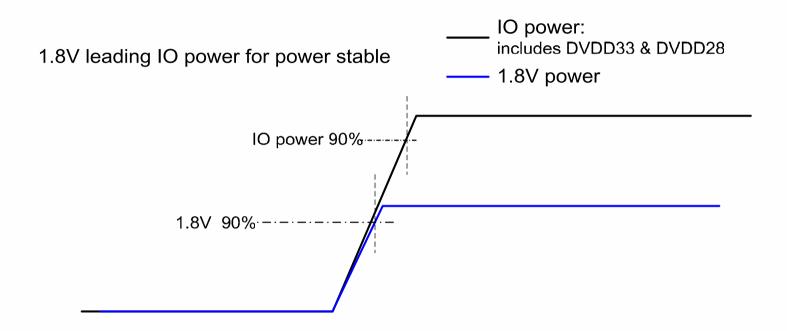

## MT5921 Power Sequence

In order to prevent from the IO driving unpredictable signals, it is recommended that the 1.8V is applied before IO power or they are applied at the same time.

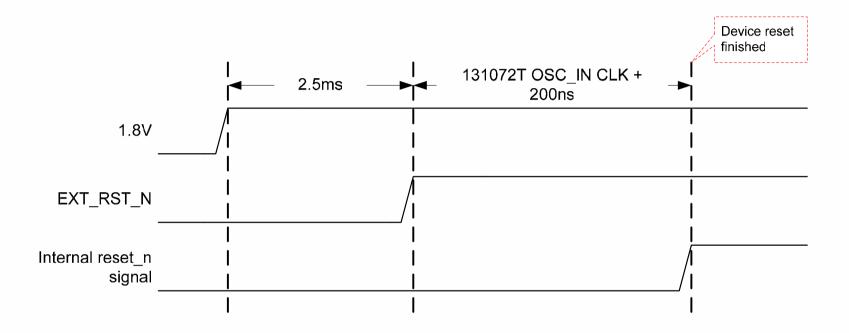

# MT5921 Power On /Reset Timing

◆The power on reset time is related to the frequency of main reference clock source. The normal functions are not ready until the power-on-reset was done.

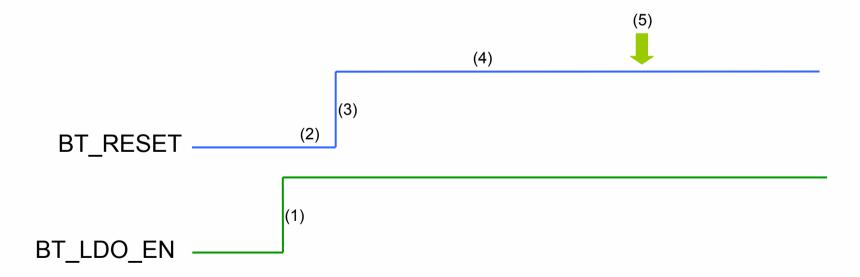

#### MT6611 Power On Initialization

- Hardware reset sequence & timing requirement

- (1) Set BT\_LDO\_EN to high

- (2) Wait for at least 2ms

- (3) Set BT\_RESET to high

- (4) Wait for at least 1000ms

- (5) MT6611 is ready for receive HCI command

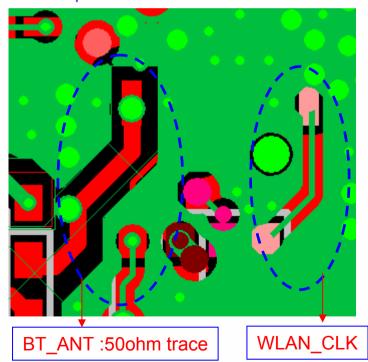

#### **Module Layout Guide – 1/4**

- Please place the bypass capacitors to the 3.3/2.8/1.8V power rail as close as possible.

- Please keep 50 ohm transmission for The WiFi/BT RF trace.

- •Please isolate the WiFi/BT main clock trace with GND

- •Please reserve the 9 square GND PAD for better performance for module

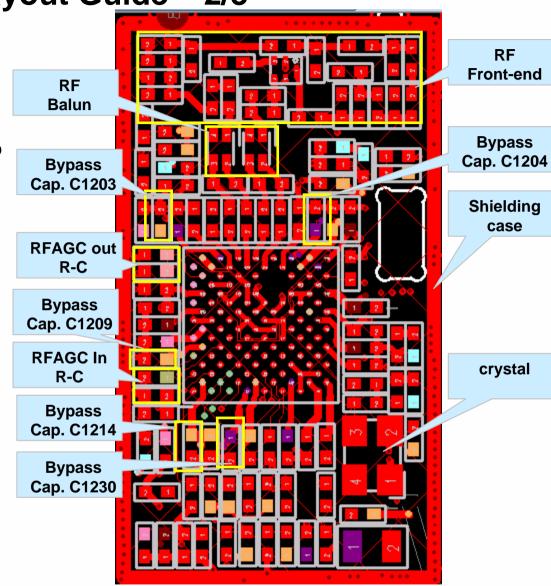

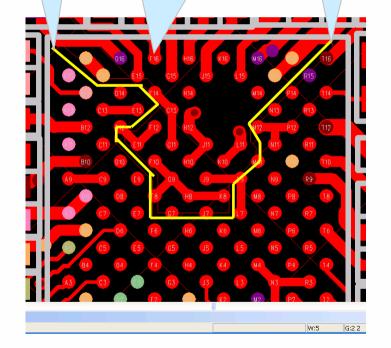

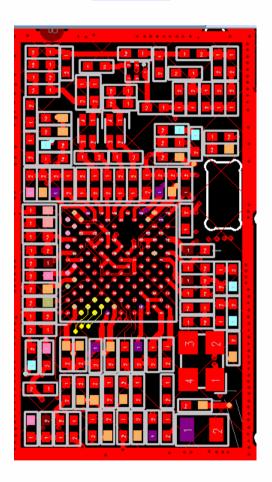

#### Layer1

#### Reference Layout – 2/4

<u>Layer1</u> <u>Layer2</u>

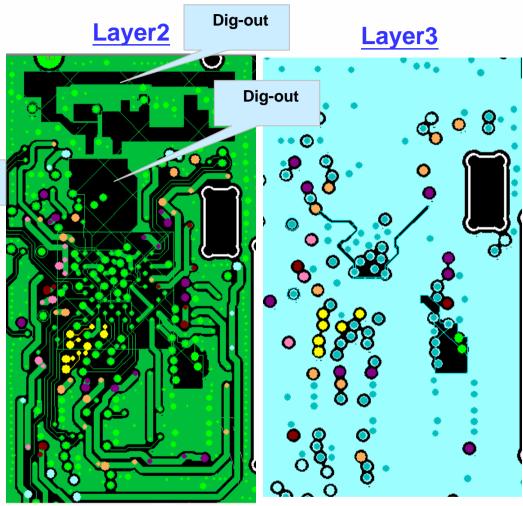

#### Reference Layout – 3/4

#### Layer3

Layer4

#### **Reference Layout – 4/4**

<u>Layer5</u> <u>Layer6</u>

#### **Module Footprint Layout Guide**

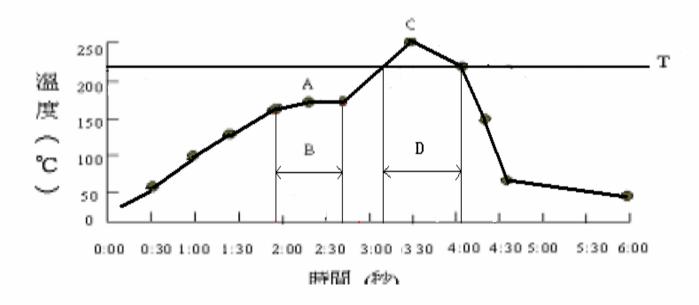

# Module SMT Reflow profile

| A. 預熱溫度 (PRE-HEAT TEMP) C:最高溫度 (FEAK TEMP)<br>B. <b>預熱時間(PRE-HEAT TIME)</b> D:T℃以上時間 (DWELL TIME AT T ℃ VARIABLE) |          |            |          |            |        |

|-------------------------------------------------------------------------------------------------------------------|----------|------------|----------|------------|--------|

| VARIABLES TYPE                                                                                                    | A        | В          | C        | D          | T      |

| LeadFree.rcp<br>(AG4無鉛Sn/Ag4/Cu).5)                                                                               | 180 ±10℃ | 40 ±10 sec | 252 ±10℃ | 45 ±10 sec | 220 °C |

# MEDIATEK

#### MT3326 Application Design Note

2009 / 04

Copyright © MediaTek Inc. All rights reserved.

## **Agenda**

- MTK GPS Overview

- MT3326 GPS Feature

- MT3326 System Block

- MTK GPS Reference Design

- MT3326 Schematic Design Note

- MT3326 PCB Design Note

- MT3326 QVL

- MT3326 Debug SOP

- MT3326 ATE Tool

- MTK GPS Tier One Performance

- Summary

- Q&A

#### MT3326 Features

#### Dimensions:

48-pin QFN lead-free package (6 x 6 x 0.85 mm)

#### Specification:

- Host-based GPS receiver

- 22 tracking/66 acquisition channel GPS receiver

- Supports WAAS/EGNOS/MSAS/GAGAN

- Supports up to 210 PRN channels

- Jammer detection and reduction

- Indoor/outdoor multi-path detection and compensation

- Supports A-GPS with FCC E911 compliance

- Maximum fix update rate up to 10 Hz

#### Reference Clock Support:

TCXO Frequency: 12.6 MHz ~ 40.0 MHz

#### Interfaces:

2 UARTs , SPI , I<sup>2</sup>C , GPIO

#### Low Power Consumption:

Acquisition mode : 39 mA

Tracking mode : 26 mA

Compact Layout Area: 12 x 12 mm

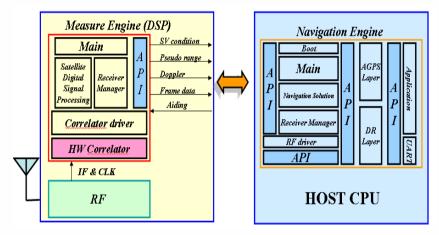

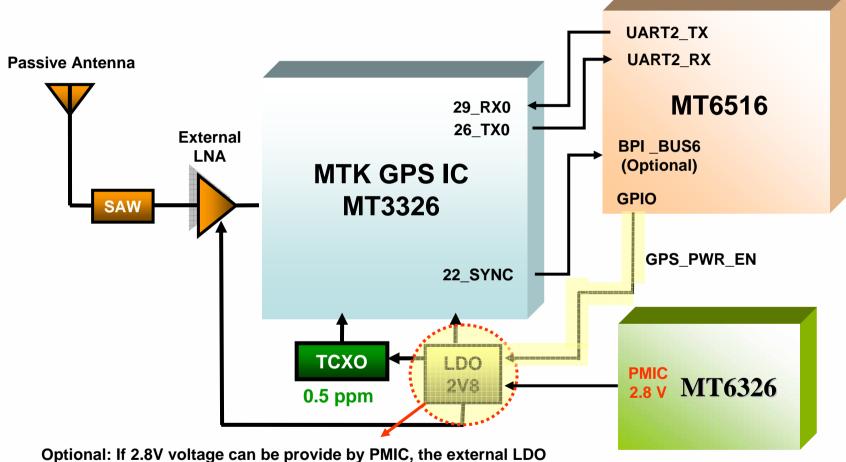

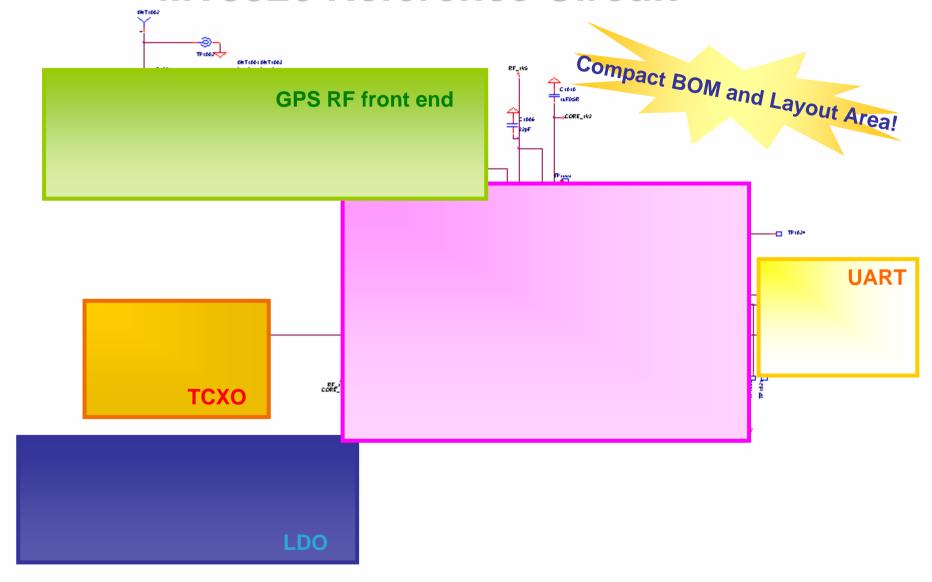

#### MT3326 Functional Blocks

Optional: If 2.8V voltage can be provide by PMIC, the external LDC can be eliminated.

- GPIO Pull Low → GPS Receiver Off

- GPIO Pull High → GPS Receiver On

Confidential B

# MEDIATEK

# MTK GPS Reference Design

Copyright © MediaTek Inc. All rights reserved.

## MTK GPS Phone Total Solution

#### Confidential B

### **Reference Design**

#### **GPS Antenna Review**

#### **Tier-1 Field Trial**

#### MTK GPS SW Build in

### **Factory Tool Support**

#### Confidential B

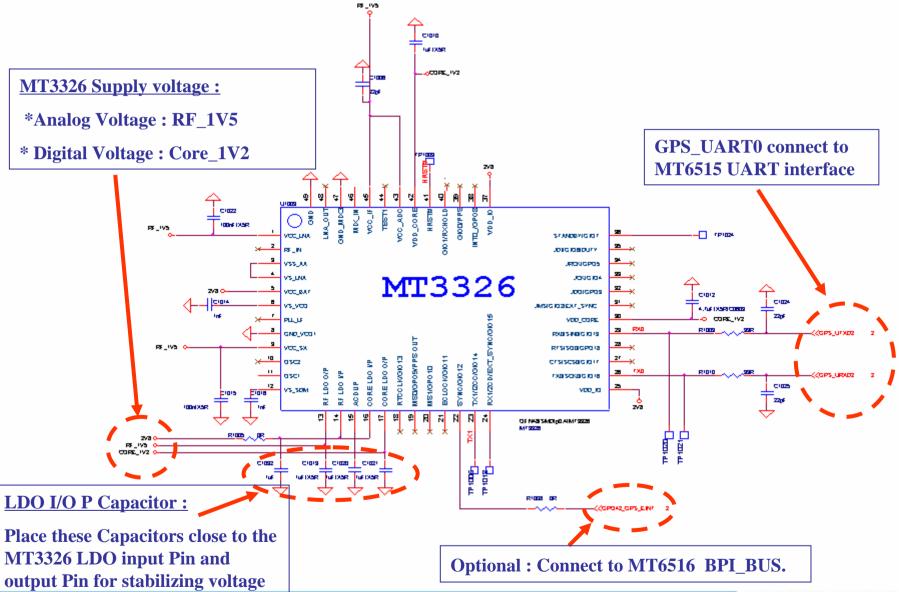

# **MT3326 Reference Circuit**

# MT3326 Reference Circuit (2/4)

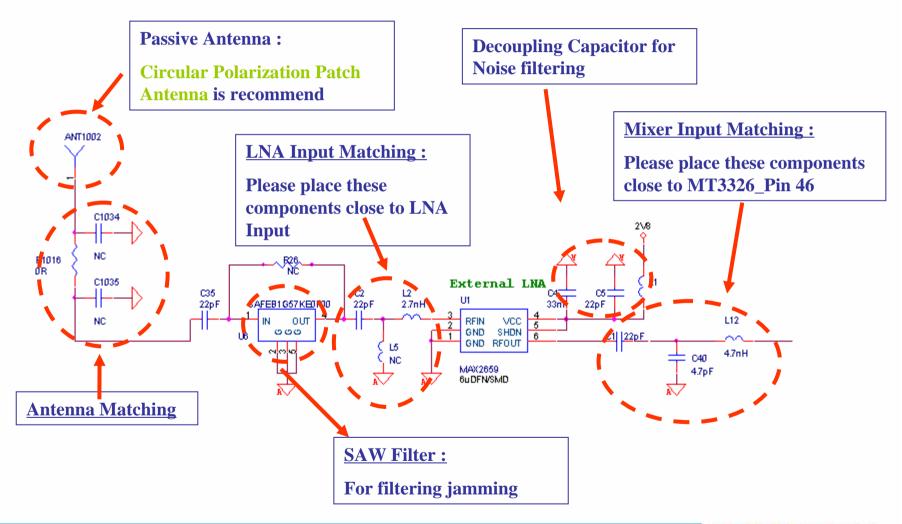

### **GPS RF Front End**

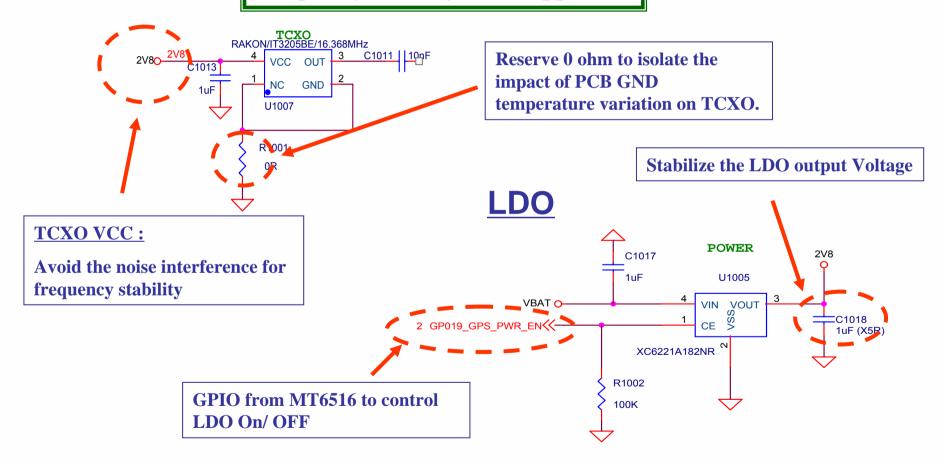

# MT3326 Reference Circuit (3/4)

Frequency:16.368 MHz

Frequency Stability: +/- 0.5ppm

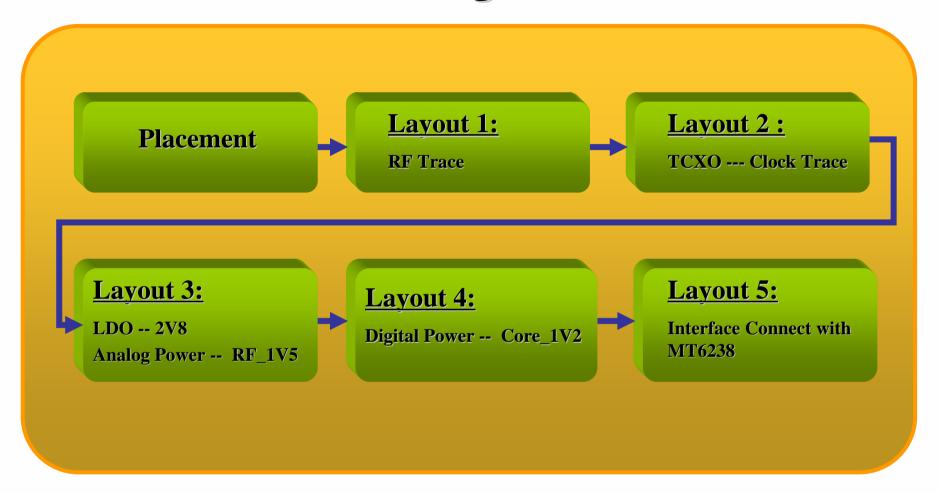

# **PCB Design Flow**

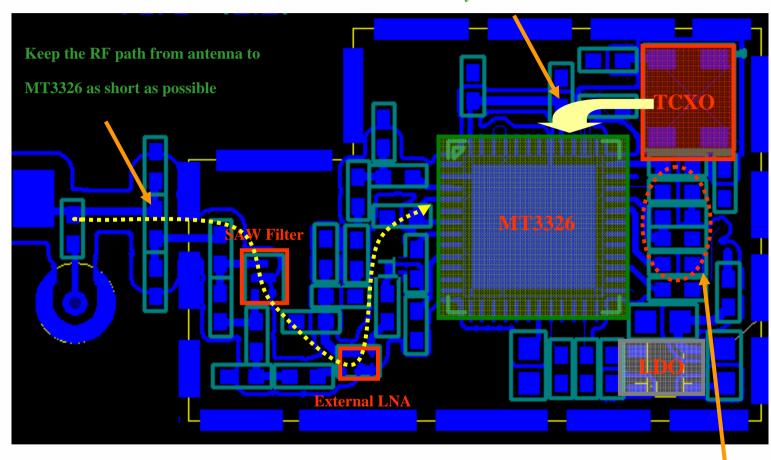

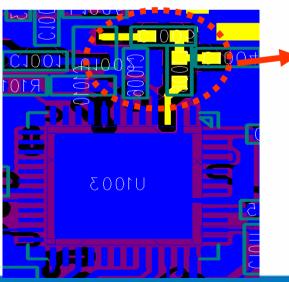

# PCB Component Placement (1/3)

The route of reference clock is the shortest to avoid interfering by other noise

The Capacitors close to analog and digital voltage output

## PCB Component Placement (2/3)

If the location of GPS function block is far away from GPS antenna Pad, please place the first-stage SAW filter and external LNA close to GPS antenna port for reducing RF path loss.

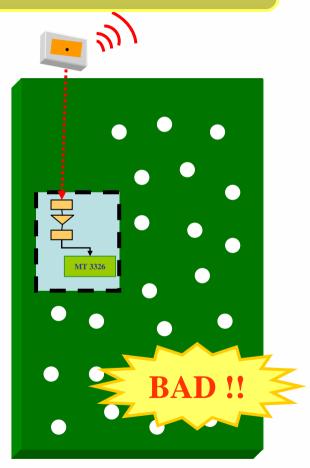

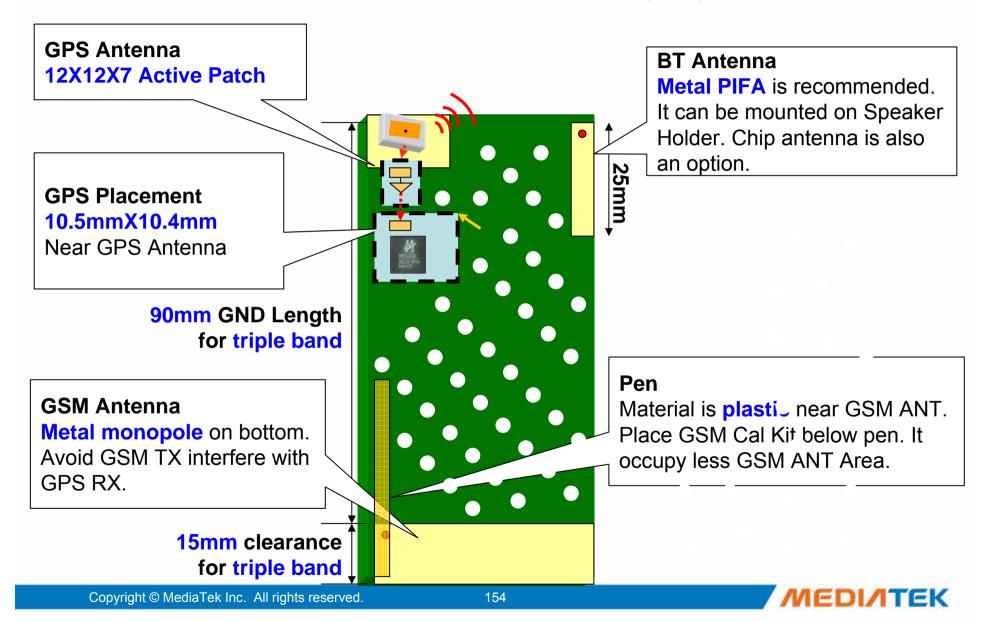

# **GPS Antenna Placement (3/3)**

#### Confidential B

### Proposal of GPS Patch Antenna for Slim Phone

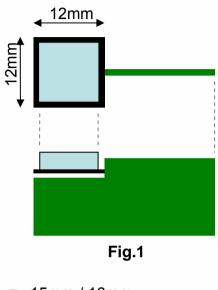

Probe-Feed RHCP Patch (Fig.1)

Patch Size: 12X12X4, 13X13X4

Vendors: Whayu, Yageo, CIRO, Microgate, Amotech

Probe-Feed LP Patch (Fig.2)

Copyright © MediaTek Inc. All rights reserved.

Patch Size: 15X10X4, 16X6X5

Vendors: Whayu, Yageo, CIRO, Microgate, Amotech

15mm / 16mm

Fig.2

### PCB Layout Design Note (1)

### • **RF Part**:

- RF Path keep as short as possible for reducing RF signal transmitted loss.

- All RF traces have to do impedance control (50 Ohm) for good sensitivity.

- RF traces route on the surface layer and far away from other high speed signal trace are recommended.

- Isolate external LNA input and output pin by copper plane.

- To keep the digital signal trace far away from the GPS layout area.

- Clear the metal below all matching component area to reduce the parasitic capacitance.

Clear the metal below the RF trace and Pad !!!

High Parasitic capacitance couldn't reach optimal RF match

# PCB Layout Design Note (2)

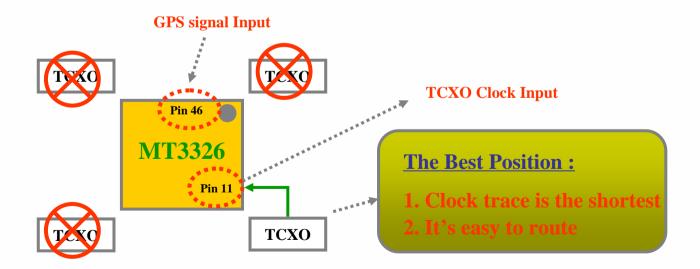

### TCXO Part:

- Keep TCXO clock trace as short as possible.

- Keep the noisy traces far away from TCXO clock traces.

- TCXO clock traces enclosed by PCB copper is recommended.

- Position TCXO far away from any high temperature component like as GSM\_PA to avoid the frequency drift.

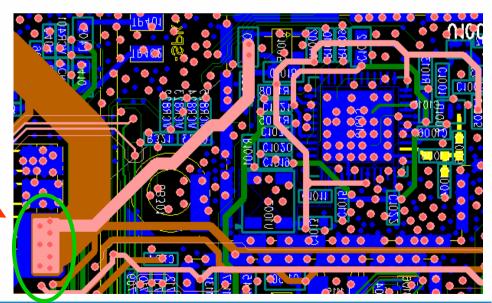

### Power Line Part

- Power trace should keep as low impedance and adequately add de-coupling capacitor for noise filtering.

- Recommended width of power trace: Main Trace: 20 mils at least

Branch into IC pin/ball: 10 mils at least

- Keep de-coupling capacitors close to the power pin of GPS chipset and external LDO.

- Use many, many via holes to connect the power traces between layers.

Use many via holes to connect the power traces between layers

# **Qualified Vender List -- TCXO**

| Component                       | Part number          | Manufacturer  | Vendor              |

|---------------------------------|----------------------|---------------|---------------------|

| TCXO (16.368 MHz)<br>+/- 0.5ppm | IT3205BE/IT3205CE    | Rakon         | Aurum Tech Inc.     |

|                                 | TTS14NSB-A8          | TEW           | Unifirst Enterprise |

|                                 | TG-5005CE-21G        | EPSON TOYOCOM | EPSON TOYOCOM       |

|                                 | 1300269-16-16.368MHz | ITTI          | ITTI                |

|                                 | KT3225F16368ACW28TA0 | Kyocera       | Kyocera             |

|                                 | ENG3090B             | NDK           | NDK                 |

|                                 | 7Q16300001-16.368MHz | TXC           | TXC                 |

| TCXO (16.368 MHz)<br>+/- 2.0ppm | TCO-5869M            | EPSON TOYOCOM | EPSON TOYOCOM       |

| TCXO 2520<br>(16.368 MHz )      | IT2205BE 16.368 MHz  | Rakon         | Aurum Tech Inc.     |

|                                 | KT2520Y16368ACW28TMA | Kyocera       | Kyocera             |

# **Qualified Vender List -- LNA & LDO**

| Component    | Part number   | Manufacturer | Vendor |

|--------------|---------------|--------------|--------|

|              | NJG1117HA8    | JRC          | 東鞍     |

| External LNA | UPC8231       | NEC          | NEC    |

|              | MAX2659       | MAXIM        | MAXIM  |

|              | XC6215/XC6401 | Torex        | 敏茜     |

| LDO_2V8      | AME8801CEEVZ  | AME          | AME    |

|              | TK71728       | токо         | 華成     |

# **Qualified Vender List -- GPS Antenna**

| Circular-Polarized Patch |                           |  |  |

|--------------------------|---------------------------|--|--|

| Antenna Vendor           | Size (mm³)                |  |  |

| Whayu                    | 12X12X4, 13X13X4, 15X15X4 |  |  |

| Yageo                    | 12X12X4, 15X15X4          |  |  |

| Mag.layers               | 15X15X4                   |  |  |

| CIRO                     | 12X12X4, 13X13X4, 15X15X4 |  |  |

| Amotech                  | 13X13X4                   |  |  |

# MT3326 HW Debug SOP

Verify voltage level of all power Supplies **Check Connection of UART** TXD & RXD Check GPS HW Configuration GPIO Setting & PMIC 2.8V **GPS Function Ok!**

### MTK GPS Phone Manufacture Flow

Confidential B **Radiation Conductive Assembly MiniGPS ATE Multi- Channel** Antenna **Single Channel PCBA** Or Open Sky Unit

**MT3326 No need!!**

FW

**Download**

Com port **Baud rate**

EK

**TTFF** and Hot Start

are good?

# Repair station

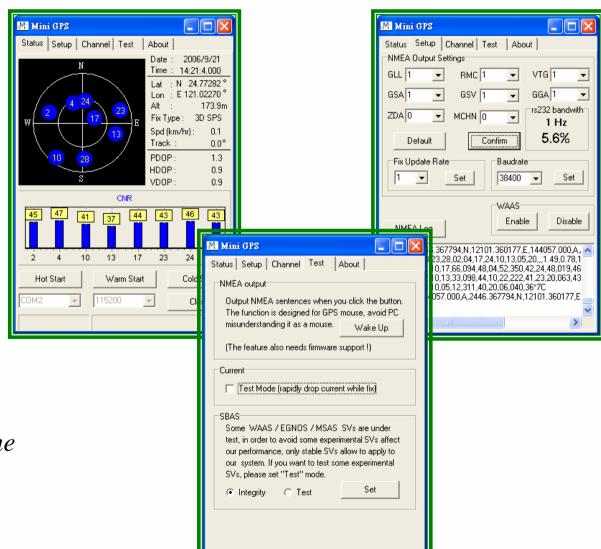

# Mini GPS Tool (PC Version)

**♦**Feature

GPS Status

TTFF Test

NMEA Output

Update Rate

Baudrate

WAAS

Log NMEA

32 Channel

Firmware Ver.

**♦**Usage

Customers

Production line

End users

# Test Instruments (1/2)

### **Multi-Channel GPS Satellite Simulation System**

**Spirent GSS6560**

### **Spirent STR4500**

# Test Instruments (2/2)

### **Areoflex**

### Single channel GPS-101 GPS Satellite Simulator

SG

NFA

Confidential B

# MEDIATEK

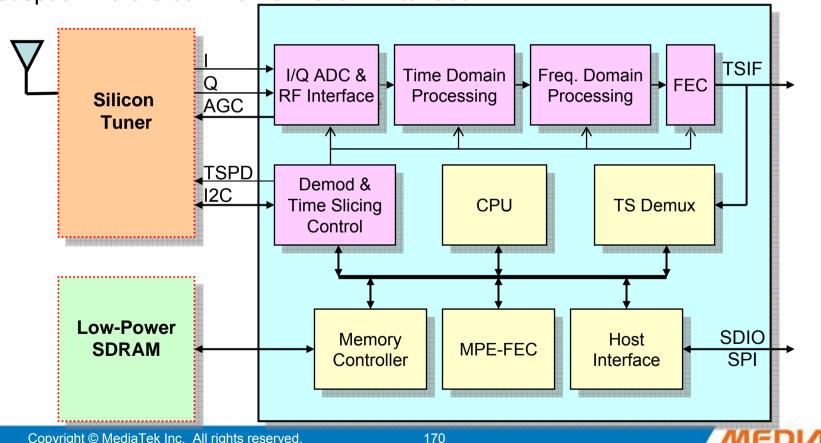

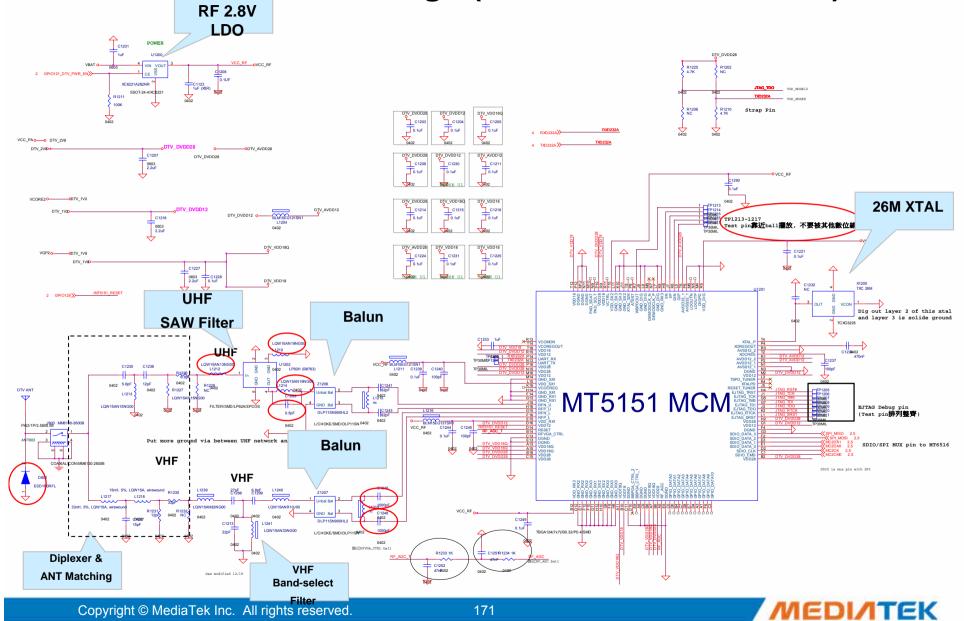

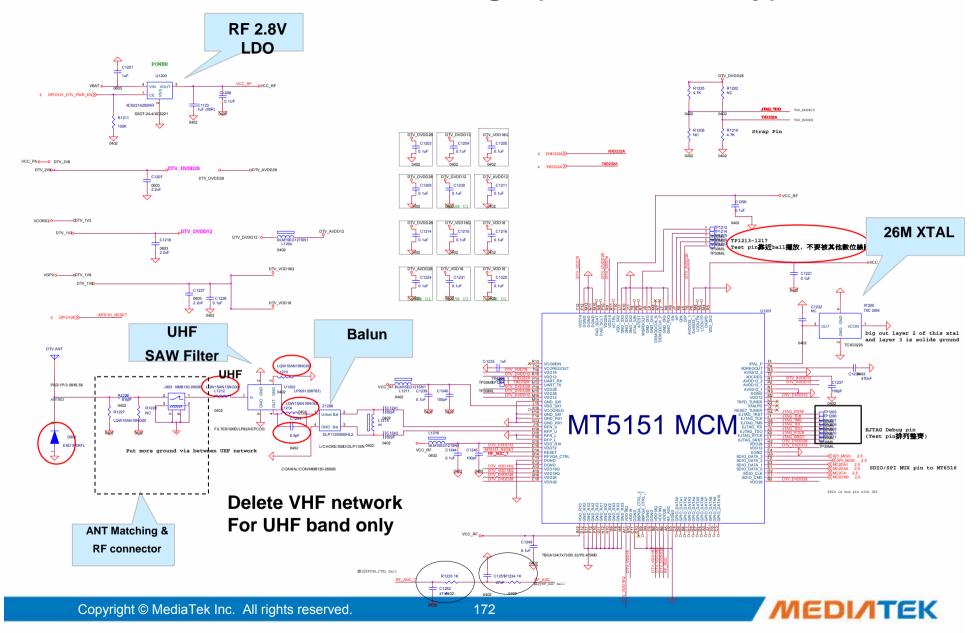

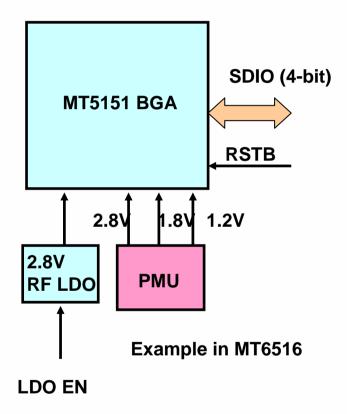

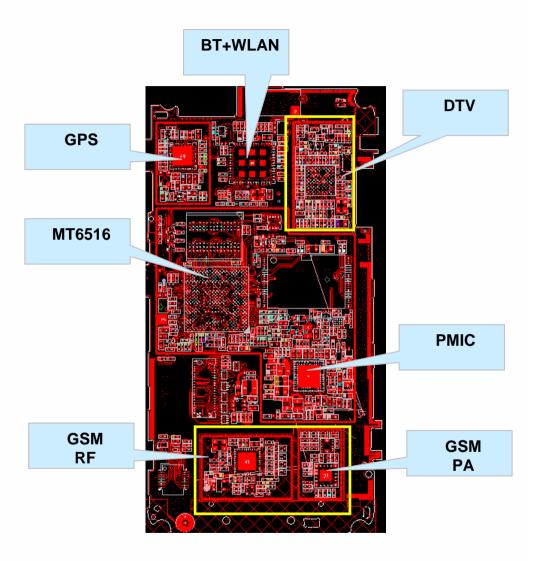

# **DTV Application Note**

$\label{local_constraints} \mbox{Copyright} @ \mbox{MediaTek Inc. All rights reserved}.$

### **Outline**

- DTV function block and reference design

- > DTV function block

- > DTV reference design

- Reference interface assignment and key component

- > Reference interface assignment

- Key component

- Schematic and layout design guide